D. ZAKHAROV, 프로코피예프, 케메 로보 지역

컴퓨터의 인터페이스 포트 제어를 마스터 한 무선 아마추어는 다양한 신호 및 작동 장치 및 센서를 컴퓨터에 연결하여 컴퓨터를 가전 제어 센터, 아파트 보안 시스템 또는 측정 장치로 전환 할 수 있습니다. 원래 프린터 컴퓨터에 연결하기위한 LPT 병렬 포트는 초보자에게 가장 적합합니다. 여기에서 약어 LPT-Line Printer Terminal (약칭 LPT-라인 프린터 터미널)이 나옵니다. 나중에이 포트의 범위가 크게 확장되면서 다양한 주변 장치가 연결되기 시작했습니다. 불행히도, 오늘날 (다른 컴퓨터 포트와 마찬가지로) 점차 고속 범용 USB 직렬 버스로 대체되고 있습니다.

컴퓨터 시스템 장치의 LPT 포트 커넥터는 25 핀 DB-25F 소켓입니다. TTL 구조 미세 회로의 레벨 특성의 논리 신호를 접점에 적용하고 제거 할 수 있습니다. 0 ... 0.8 V의 전압은 논리적으로 낮고 높은-2.4 ... 5 V로 간주됩니다. 커넥터의 출력 접점을 공통 와이어 또는 +5 V를 초과하지 않는 전압 소스로 연결하십시오. 저항이 300 이상인 저항을 통해서만 권장됩니다 옴 포트의 입력 또는 출력에는 5V 이상의 음의 전압 또는 양의 전압을인가 할 수 없으며 컴퓨터가 220V 네트워크에서 완전히 분리 된 경우에만 포트에 연결하고 연결을 끊을 수 있습니다 (전원 플러그가 소켓에서 분리됨). 연결된 장치의 전원이 켜져 있으면 네트워크에서 물리적으로 연결이 끊어 져야합니다.

이러한 요구 사항을 준수하지 않으면 심각한 결과를 초래할 수 있습니다. 컴퓨터 내부의 병렬 포트 컨트롤러 칩이 고장 나면 마더 보드를 수리하거나 교체해야합니다.

컴퓨터를 켜면 병렬 포트가 Centronics 모드에서 작동합니다.이 포트는 컴퓨터에 나타난 이후 가장 단순하고 전통적인 포트입니다. 이 모드를 SPP (Simple Parallel Port)라고도합니다. 일반적으로 레이저 프린터 및 스캐너와의 고속 정보 교환을 위해 더 복잡한 EPP 및 ECP 모드가 사용됩니다. 그러한 모드에서 포트로 작업을 프로그래밍하는 것은 숙련 된 프로그래머 만 사용할 수 있기 때문에 우리는이를 고려하지 않을 것입니다.

프로그램 관점에서 Centronics 모드의 LPT 포트는 마이크로 프로세서 I / O 공간에 3 개의 8 비트 레지스터를 나타냅니다. DR 데이터 레지스터는 & H378, SR 프린터 상태 레지스터는 & H379, CR 프린터 제어 레지스터는 & H37A입니다. 표시된 주소는 일반적으로 컴퓨터에서 유일한 LPT1 포트를 나타냅니다. 다른 병렬 포트가 있으면 연속 된 주소를 가진 세 개의 레지스터가 할당됩니다. 예를 들어, LPT2 포트 레지스터에는 일반적으로 주소 & H278- & H27A가 있습니다.

포트 레지스터의 입력과 출력은 (모두는 아니지만) 인터페이스 커넥터의 접점에 연결됩니다. 1.

따라서 이러한 레지스터에 특정 코드를 작성하면 커넥터의 출력 접점에서 해당 논리 전압 레벨을 설정하고 레지스터에서 코드를 읽고 입력에 공급되는 외부 신호의 레벨을 결정할 수 있습니다.

거의 모든 프로그래밍 환경 및 운영 체제에서 LPT 포트로 작업 할 수 있습니다. Visual Basic과 Delphi는 가장 접근하기 쉬운 환경으로 간주되며 포트 프로그래밍에 필요한 모든 환경은 매우 유사합니다. 최신 멀티 태스킹 운영 체제 (Windows 제품군 포함)는 컴퓨터 응용 프로그램에서 응용 프로그램 포트로의 직접 액세스를 허용하지 않습니다. 실수로 같은 포트에 동시에 액세스하는 경우 동시에 실행되는 프로그램 간의 충돌을 피하기 위해 수행됩니다. 포트와의 통신은 충돌을 해결하는 데 필요한 모든 것을 자동으로 수행하는 특수 드라이버 프로그램을 통해서만 가능합니다. 프로그래머는 몇 가지 제어 명령 만 작성할 수 있습니다.

우리는 인터넷에서 쉽게 찾을 수있는 두 번째 버전의 Inpout32.dll과 같은 프로그램 중 가장 인기있는 라이브러리 중 하나를 사용합니다. 다양한 프로그래밍 환경 및 운영 체제에 적용 할 수 있습니다. Windows 98에서 lnpout32.dll 파일을 C : \\ Windows \\ system \\ 폴더로 복사하고 Windows XP에서 C : \\ Windows \\ system32 \\ 폴더로 복사해야합니다. 대부분의 경우이 파일을 실행 가능 프로그램 폴더에 두는 것만으로 충분합니다. DOS에서의 프로그래밍에는 추가 드라이버가 필요하지 않으며, 사용 된 프로그래밍 언어로 제공된 포트에 대한 일반적인 입력 / 출력 명령으로 충분합니다.

다음 설명은 Windows XP를 실행하는 Visual Basic 6.0 프로그래밍 시스템에서 병렬 포트를 사용한 작업과 관련이 있습니다. 개발을 위해 간단한 프로그램이 개발되었습니다. 실행 파일 test.exe 및 기본 (및 유일한) Form1.frm 파일을 포함한 그녀의 프로젝트가 기사에 첨부됩니다. 이 프로그램을 실행하면 그림 1과 같은 창이 나타납니다. 2.

온 스크린 버튼을 클릭하고 해당 필드에 숫자를 입력하면 포트 출력에서 \u200b\u200b전압 레벨을 설정하고 입력 상태를 읽을 수 있습니다 (해당 필드에 숫자로 표시됨). LPT 포트로 작업하기위한 라이브러리는 표에 표시된 Form1.frm 파일의 조각을 프로그램에 "연결"합니다.

먼저 CR 제어 레지스터를 사용하여 작업을 분석합니다 (주소는 & H37A입니다). 고려중인 경우 서브 루틴에 의해 수행됩니다.

프라이빗 서브 커맨드 4_click ()

out & H37A, Text2.Text

엔드 서브

화면상의 Command4 버튼 ( "Submit")을 누르면이 버튼 위의 필드에 입력 된 10 진수에 해당하는 2 진 코드가 & H37A의 레지스터에 기록됩니다.

명확성을 위해 그림 1에 표시된 회로에 따라 LED 노드를 LPT 커넥터에 조립하고 연결합니다. 3.

필요한 필드에 숫자 4 (2 진 00000100)를 입력하고 "보내기"버튼을 클릭하십시오. 그런 다음 네 개의 LED가 모두 켜집니다. 실제로 CR, CR 및 CR 방전은 인버터를 통해 커넥터 핀에 연결되므로 이러한 방전에 0을 쓸 때 해당 접점의 레벨이 높아졌습니다. HL3 LED 만 켜려면 숫자 15 (2 진 00001111)를 입력해야하며 숫자 11 (2 진 0001011)을 입력하면 모든 LED가 꺼집니다. 제어 레지스터 (CR-CR)의 상위 비트는 커넥터 핀에 연결되어 있지 않으므로이 상태는 중요하지 않습니다.

SR 상태 레지스터의 작동을 연구하기 위해 노드를 포트 커넥터에 연결합니다.이 회로는 그림 1에 나와 있습니다. 4.

회로 차단기 SA1-SA5가 열리면 저항 R1-R5를 통해 커넥터 접점에 높은 로직 레벨 전압이 적용됩니다. 소스는 출력 전압 5V, 3 개의 갈바니 셀 배터리 및 LPT 포트의 출력 중 하나를 포함하는 네트워크 어댑터 일 수 있으며, LPT 포트의 출력 중 하나는 필요한 전압 레벨이 앞에서 설명한 방법을 사용하여 설정됩니다. 많은 컴퓨터에서 R1-R5와 유사한 저항이 이미 사용 가능하므로 이러한 경우 외부 저항을 설치할 필요가 없습니다.

"Accept"소프트 키를 클릭하면 서브 루틴이 실행됩니다

개인 하위 명령 5_c1ick ()

Text3.Text \u003d Inp (& H379)

엔드 서브

SR 레지스터의 내용을 표시하는 숫자가 버튼 위의 상자에 표시됩니다. 모든 스위치 (그림 4)가 열려 있으면 126 (이진 01111110)이며 닫혀 있으면 134 (10000110)입니다. SR-SR 비트의 값은 커넥터의 해당 접점에 공급되는 레벨에 해당하며 SR 방전의 값은 핀 11의 레벨에 반비례합니다. SR-SR의 최하위 비트가 커넥터에 출력되지 않으므로 해당 값은 접점에 적용된 신호에 의존하지 않습니다.

메인 포트 레지스터는 & H378의 DR 데이터 레지스터입니다. 인쇄 된 정보는 프린터로 바이트 전송됩니다. 레지스터의 8 비트는 모두 커넥터 핀에 연결되며 인버터는 없습니다. 이 8 개의 회로는 종종 "데이터 버스"라는 이름과 결합됩니다. 초기 상태에서는 출력에서만 작동합니다. 그러나 거의 모든 최신 컴퓨터는 8 비트 이진 코드의 병렬 입력으로 컴퓨터를 전환 할 수 있습니다. 이를 위해서는 제어 레지스터의 CR 범주에 장치를 작성하는 것으로 충분합니다.

불행히도 Centronics 모드에서는 LPT 포트의 데이터 버스가 작동하는 방향에 대한 신호가 없으며 해당 커넥터가 출력되지 않습니다. 따라서 프로그래밍 된 "수신"전환이 완료된 후에 만이 버스에 특별한주의를 기울이고 외부 신호를 공급해야합니다. 그렇지 않으면 컴퓨터 자체와 포트에 연결된 신호 소스의 인터페이스 미세 회로가 손상 될 수 있습니다. 병렬 포트 데이터 버스를 통한 정보 전송 방향에 대한 완전한 제어 신호 세트가 제공되는 EPP 및 ECP 모드에서는 이러한 단점이 제거되었습니다.

고려중인 테스트 프로그램에서 서브 루틴은 데이터 레지스터와 함께 작동합니다.

프라이빗 서브 커맨드 3_ 클릭 ()

Out & H378, Text1.Text

Text1.Text \u003d Inp (& H378)

엔드 서브

"OK"화면 버튼을 클릭하면 버튼 위의 필드에서 번호를 데이터 레지스터에 쓴 다음 레지스터의 내용을 읽고 동일한 필드에 표시합니다. 당연히 레지스터가 출력으로 작동하는 경우 ( "전송"항목이 화면에 표시됨) 필드의 숫자는 동일하게 유지됩니다. 이 경우 포트 커넥터의 핀 2–9의 로직 레벨이 수동으로 필드에 입력되고 데이터 레지스터에 기록 된 번호와 일치하도록하려면 그림 1과 유사한 커넥터에 노드를 연결하십시오. 3 개이지만 LED와 저항기 수가 8 개로 증가했습니다.

데이터 버스를 입력으로 전환하는 작업은 서브 루틴에 의해 수행됩니다.

개인 하위 옵션 1_ 클릭 ()

아웃 & H37A, 32

엔드 서브

종속 잠금 "수신"으로 화면 버튼을 클릭하면 통화가 발생합니다. "전송"버튼을 사용하여 유사한 서브 루틴이 호출되는데, 이는 32 (2 진 00100000)가 아니라 0으로 제어 레지스터에 기록하는 것만 다릅니다. 따라서 데이터 버스를 출력 모드로 되돌립니다.

데이터 버스가 입력 모드로 전환되면 "OK"버튼을 눌렀을 때 호출 된 이전에 고려 된 서브 루틴의 출력 절차가 실제로 작동하지 않습니다. 그러나 Inp 기능은 연결된 외부 회로에 의해 설정된 핀 2-9의 레벨에 해당하는 값을 반환합니다. 10 진수로 확인 버튼 위의 상자에 나타납니다. 상태 레지스터 작업에 사용되는 노드와 유사한 노드를 사용하여 데이터 버스 라인에서 논리 레벨을 설정할 수 있습니다 (그림 4).

프로그램을 복잡하게 만들지 않기 위해 "수신"및 "전송"버튼을 사용한 제어 레지스터 상태 변경은 "송신"버튼 위의 입력 필드에 표시되지 않습니다.

이 기사에서 주어진 예제를 마스터하면서 포트를 통해 컴퓨터에서 12를 출력하고 5 개의 논리 신호를 출력하거나 (다른 모드에서) 4를 출력하고 13의 신호를 입력하는 방법을 배웠습니다. 이제 LPT 포트를 통해 컴퓨터에 연결하는 훨씬 더 복잡한 프로그램 및 장치를 개발할 수 있습니다.

편집자로부터. 이 기사에서 언급 한 파일 및 테스트 프로그램 작업에 필요한 기타 파일은 FTP 서버 (ftp://ftp.radio.ru/pub/2007/09/testlpt.zip)에 있습니다.

라디오 2007 №9

프린터에 연결하기 위해 병렬 인터페이스 포트가 PC에 도입되었으므로 이름은 LPT 포트 (Line PrinTer-라인 프린터)입니다. 기존의 표준 LPT 포트 (소위 SPP 포트)는 데이터 출력에 중점을 두지 만 일부 제한 사항으로 데이터를 입력 할 수 있습니다. 양방향, EPP, ECP 등 LPT 포트의 다양한 수정이 있으며 기능을 확장하고 생산성을 높이며 프로세서의 부하를 줄입니다. 처음에는 개별 제조업체의 브랜드 솔루션이었으며 나중에 IEEE 1284 표준이 채택되었습니다.

외부에는 포트에 8 비트 데이터 버스, 5 비트 상태 신호 버스 및 DB-25S 소켓으로 출력되는 4 비트 제어 신호 버스가 있습니다. LPT 포트는 TTL 로직 레벨을 사용하는데, 이는 TTL 인터페이스의 낮은 노이즈 내성으로 인해 허용 가능한 케이블 길이를 제한합니다. 전기 절연은 없습니다. 연결된 장치의 회로 접지가 컴퓨터의 회로 접지에 연결되어 있습니다. 이로 인해 포트는 장치 연결 및 접지 규칙을 위반하는 컴퓨터 취약점입니다. 포트는 일반적으로 마더 보드에 있기 때문에 타 버린 경우 전체 마더 보드가 타 버릴 때까지 주변 환경이 실패하는 경우가 많습니다.

소프트웨어 측면에서 LPT 포트는 I / O 공간에있는 레지스터 모음입니다. 포트 레지스터는 포트의 기본 주소를 기준으로 주소가 지정되며 표준 값은 3BCh, 378h 및 278h입니다. 포트는 하드웨어 인터럽트 요청 라인 (일반적으로 IRQ7 또는 IRQ5)을 사용할 수 있습니다. 고급 모드에서는 DMA 채널도 사용할 수 있습니다.

이 포트는 BIOS 수준에서 지원합니다. POST 테스트 및 Int 17h 인쇄 서비스 (8.3.3 절 참조) 중에 설치된 포트 검색은 하드웨어 출력을 사용하지 않고 준비 스캔을 통해 문자 출력, 인터페이스 및 프린터 초기화 및 폴링을 제공합니다. 프린터 상태. 거의 모든 최신 마더 보드 (486 프로세서 용 PCI 보드로 시작)에는 LPT 포트 어댑터가 통합되어 있습니다. LPT 포트가있는 ISA 카드가 있으며 여기에는 디스크 인터페이스 컨트롤러 (FDC + IDE)뿐만 아니라 COM 포트 쌍과 공존하는 경우가 많습니다. LPT 포트는 일반적으로 디스플레이 어댑터 보드 MDA (모노크롬 텍스트) 및 HGC (모노크롬 그래픽 "Hercules")에 있습니다. 추가 LPT 포트가있는 PCI 카드가 있습니다.

전자 키, 프로그래머 및 기타 장치뿐만 아니라 프린터, 플로터, 스캐너, 통신 장치 및 데이터 저장 장치가 LPT 포트에 연결됩니다. 때때로 두 컴퓨터 간의 통신에 병렬 인터페이스가 사용됩니다. 네트워크가 "무릎을 꿇고"(LapLink) 만들어졌습니다.

1.1. 전통적인 LPT 포트

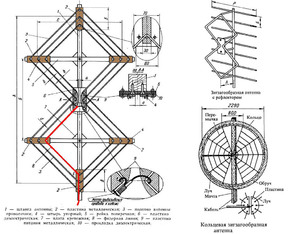

일명 표준 LPT 포트는 표준 병렬 포트 (SPP) 또는 SPP 포트라고하며 Centronics 교환 프로토콜이 소프트웨어로 구현되는 단방향 포트입니다 (8.3.1 절 참조). 포트 커넥터 신호 (표 1.1)의 이름과 목적은 Centronics 인터페이스에 해당합니다.

표 1.1. 표준 LPT 포트 커넥터

| DB-25S 문의 | 케이블 와이어 번호 | 약속 I / O¹ | 비트 ² | 신호 |

| 1 | 1 | 오 / 난 | CR.0 | 스트로브 # |

| 2 | 3 | O (I) | DR.0 | 데이터 0 |

| 3 | 5 | O (I) | DR.1 | 데이터 1 |

| 4 | 7 | O (I) | DR.2 | 데이터 2 |

| 5 | 9 | O (I) | DR.3 | 데이터 3 |

| 6 | 11 | O (I) | DR.4 | 데이터 4 |

| 7 | 13 | O (I) | DR.5 | 데이터 5 |

| 8 | 15 | O (I) | DR.6 | 데이터 6 |

| 9 | 17 | O (I) | DR.7 | 데이터 7 |

| 10 | 19 | I³ | SR.6 | 승인 번호 |

| 11 | 21 | 나 | SR.7 | 바쁜 |

| 12 | 23 | 나 | Sr.5 | 페이퍼 엔드 (PE) |

| 13 | 25 | 나 | SR.4 | 선택 |

| 14 | 2 | 오 / 난 | CR.1 | 자동 LF # (자동 공급 #) |

| 15 | 4 | 나 | SR.3 | 오류 # |

| 16 | 6 | 오 / 난 | CR.2 | 초기화 # |

| 17 | 8 | 오 / 난 | CR.3 | #에서 선택 |

| 18-25 | 10, 12, 14, 16, 18, 20, 22, 24, 26 | - | - | - |

¹ I / O는 포트 신호의 전송 방향 (입력-출력)을 설정합니다. O / I는 출력 포트에서 읽을 때 상태를 읽는 출력 라인을 나타냅니다. O (I)-출력 라인-상태는 특수 조건에서만 읽을 수 있습니다 (아래 참조).

² 반전 된 신호에는 "\\"가 표시됩니다 (레지스터의 1은 로우 라인 레벨에 해당).

³ 입력 Ack #은 저항 (10kOhm) ~ + 5V로 연결됩니다.

SPP 포트 어댑터에는 BASE 포트의 기본 주소 (3BCh, 378h 또는 278h)에서 시작하여 I / O 공간의 인접한 주소에 3 개의 8 비트 레지스터가 있습니다.

데이터 레지스터 (DR)-데이터 레지스터, 주소 \u003d BASE 이 레지스터에 기록 된 데이터는 데이터 출력 라인으로 출력됩니다. 어댑터 회로에 따라이 레지스터에서 읽은 데이터는 이전에 기록 된 데이터 또는 동일한 라인의 신호에 해당하며 항상 같은 것은 아닙니다.

상태 레지스터 (SR)-상태 레지스터 (읽기 전용), 주소 \u003d BASE + 1 레지스터는 5 비트 프린터 상태 신호 입력 포트 (비트 SR.4-SR.7) 및 인터럽트 플래그를 표시합니다. SR.7 비트가 반전됩니다. 낮은 신호 레벨은 레지스터의 단일 비트 값에 해당하며 그 반대도 마찬가지입니다.

상태 레지스터 비트의 목적은 아래에 설명되어 있습니다 (괄호 안에는 포트 커넥터의 핀 번호가 있습니다).

♦ SR.7-Busy-Busy 회선 상태의 역상 표시 (11) : 회선의 낮은 수준에서 단일 비트 값이 설정되어 다음 바이트를 출력 할 수 있습니다.

♦ SR.6-Ack (Acknowledge)-Ack # 라인의 상태를 표시합니다 (10).

♦ SR.5-PE (용지 끝)-용지 끝 라인 (12)의 상태를 표시합니다. 단일 값은 프린터의 용지 끝에 대한 신호 인 높은 수준의 선에 해당합니다.

♦ SR.4-선택-선택 라인 (13)의 상태를 표시합니다. 단일 값은 프린터의 전원을 켜는 신호 인 높은 회선 수준에 해당합니다.

♦ SR.3-오류-오류 번호 (15)의 상태를 표시합니다. 값이 0이면 프린터 오류 신호 인 로우 라인에 해당합니다.

♦ SR.2-PIRQ-Ack # 인터럽트 플래그 (PS / 2 포트만 해당). Ack # 신호로 인해 하드웨어 인터럽트가 발생하면 비트가 재설정됩니다. 단위 값은 하드웨어 리셋 및 상태 레지스터를 읽은 후 설정됩니다.

♦ SR-예약 됨

제어 레지스터 (CR)-제어 레지스터, 주소 \u003d BACE + 2, 쓰기 및 읽기가 가능합니다. 레지스터는 판독이 가능한 제어 신호 (비트 0-3)의 4 비트 출력 포트에 연결됩니다. 출력 버퍼는 일반적으로 오픈 콜렉터 유형입니다. 이를 통해이 레지스터의 라인을 하이 레벨로 프로그래밍 할 때 입력으로 올바르게 사용할 수 있습니다. 비트 0, 1, 3이 반전됩니다.

제어 레지스터 비트의 목적은 다음과 같습니다.

♦ CR-예약되었습니다.

♦ CR.5-방향-전송 방향을 제어하기위한 비트 (PS / 2 포트만 해당, 아래 참조). 장치 레코드는 데이터 포트를 입력 모드로 설정합니다. 읽을 때 비트 상태는 정의되지 않습니다.

♦ CR.4-AckINTEN (Ack Interrupt Enable)-단일 값은 라인 Ack #의 신호 감소에 대한 중단을 허용합니다. 다음 바이트에 대한 요청 신호.

♦ CR.3-Select In-단일 비트 값이 출력 Select In # (17)에서 로우 레벨에 해당합니다.이 신호는 프린터가 Centronics 인터페이스에서 작동 할 수 있도록하는 신호입니다.

♦ CR.2-초기화-0 비트 값은 출력 초기화 번호 (16)-프린터 하드웨어 재설정 신호의 하위 레벨에 해당합니다.

♦ CR.1-자동 LF-단일 비트 값은 출력 자동 LF # (14)에서 낮은 레벨에 해당합니다. 캐리지 리턴 바이트 (CR)를 수신하면 자동 라인 피드 (LF-라인 피드)를위한 신호입니다. 때때로 신호와 비트를 AutoFD 또는 AutoFDXT라고합니다.

♦ CR.0-Strobe-단일 비트 값은 Strobe # (1)의 출력에서 \u200b\u200b낮은 레벨에 해당합니다. 출력 데이터를 게이팅하기위한 신호입니다.

CR.4 \u003d 1로 설정할 때 인터페이스 커넥터 (Ack #)의 핀 10에서 음의 신호 강하에 의해 하드웨어 인터럽트 요청 (일반적으로 IRQ7 또는 IRQ5)이 생성됩니다. 잘못된 중단을 피하기 위해 핀 10은 저항에 의해 + 5V 버스에 연결되며 프린터가 이전 바이트의 수신을 확인하면 인터럽트가 생성됩니다. 이미 언급했듯이 BIOS는이 인터럽트를 사용하거나 서비스하지 않습니다.

Centronics 인터페이스의 바이트 출력 절차 단계는 필요한 프로세서 버스 작업 수를 나타냅니다.

1. 데이터 레지스터로 바이트 출력 (1 사이클 IOWR #).

2. 상태 레지스터에서 들어가서 장치의 준비 상태를 확인합니다 (비트 SR.7-통화 중 신호). 이 단계는 준비 될 때까지 또는 프로그램 시간 초과 (최소 1 IORD #주기) 전에 반복됩니다.

3. 준비 상태가되면, 데이터 스트로브는 제어 레지스터로 출력되어 설정되고 스트로브는 다음 출력으로 제거됩니다. 일반적으로 하나의 비트 (스트로브) 만 전환하기 위해 제어 레지스터가 미리 읽혀져 두 개의 IOWR #주기에 또 다른 IORD #주기가 추가됩니다.

1 바이트 출력의 경우 포트 레지스터를 사용하는 4–5 I / O 작업이 필요하다는 것을 알 수 있습니다 (가장 좋은 경우 상태 레지스터를 처음 읽음으로써 준비 상태가 감지되는 경우). 이로 인해 표준 포트를 통한 출력의 주요 단점 인 프로세서 부하가 큰 낮은 환율이 발생합니다. 포트는 프로세서가 완전히로드 될 때 오버 클럭을 100-150 Kb / s의 속도로 관리하므로 레이저 프린터로 인쇄하기에 충분하지 않습니다. 또 다른 기능 단점은 입력 포트로 사용하기가 어렵다는 것입니다.

표준 포트는 비대칭입니다. 출력에 정상적으로 작동하는 12 개의 라인 (및 비트)이있는 경우 5 개의 상태 라인 만 입력에 작동합니다. 대칭 양방향 통신이 필요한 경우 모든 표준 포트에서 니블 모드를 사용할 수 있습니다. Hewlett Packard Bi-tronics라고도하는이 모드에서는 동시에 4 비트의 데이터가 수신되며 다섯 번째 줄은 승인에 사용됩니다. 따라서 각 바이트는 두 번의 주기로 전송되며 각주기에는 5 번 이상의 I / O 작업이 필요합니다.

LPT 포트의 출력 데이터 버퍼 회로는 매우 다양합니다. 많은 구형 어댑터 모델에서 SPP 데이터 포트를 사용하여 입력을 구성 할 수도 있습니다. 모든 숫자의 단위를 가진 바이트를 데이터 포트에 쓰고 "오픈 콜렉터"유형의 출력을 가진 마이크로 회로를 통해 인터페이스의 출력 라인에 일부 코드를 보내거나 (또는 \u200b\u200b키가있는 일부 라인을 회로 접지에 연결)이 코드를 읽을 수 있습니다 동일한 데이터 레지스터에서. 그러나, 정보 전송기의 출력 회로는 어댑터 출력 버퍼의 논리 유닛의 출력 전류와 "싸워야"한다. TTL 회로는 이러한 솔루션을 금지하지는 않지만 외부 장치가 CMOS 칩을 기반으로하는 경우이 버스 충돌을“승리”하기에 전력이 충분하지 않을 수 있습니다. 그러나 최신 어댑터는 종종 출력 회로에 최대 50ohm의 저항을 갖는 종단 저항을 가지고 있습니다. 접지로의 출력의 출력 단락 전류는 일반적으로 30mA를 초과하지 않습니다. 간단한 계산은 "장치"가 출력 될 때 커넥터 접점이 접지에 단락되는 경우에도이 저항에서 1.5V의 전압이 떨어지며 이는 수신기의 입력 회로에 의해 "장치"로 해석됩니다. 따라서이 입력 방법이 모든 컴퓨터에서 작동한다고 가정 할 수 없습니다. 일부 구형 포트 어댑터에서는 보드의 점퍼에 의해 출력 버퍼가 비활성화됩니다. 그런 다음 포트는 일반 입력 포트로 바뀝니다.

1.2. 병렬 포트 확장

표준 포트의 단점은 PS / 2 컴퓨터에 나타나는 새로운 포트 유형을 부분적으로 제거했습니다.

양방향 포트 1 (Tour 1 병렬 포트)-PS / 2에 도입 된 인터페이스 이러한 포트는 표준 모드 외에도 입력 모드 또는 양방향 모드에서 작동 할 수 있습니다. 교환 프로토콜은 프로그래밍 방식으로 생성되며 전송 방향을 나타내는 특수 비트 CR.5가 포트 제어 레지스터에 입력됩니다. 0-데이터 버퍼가 출력되고 1이 입력됩니다. 이 포트 (향상된 양방향이라고도 함)를 EPP와 혼동하지 마십시오. 이 유형의 포트는 일반 컴퓨터에서도 뿌리를 내 렸습니다 .CMOS 설정에서는 PS / 2 또는 Bi-Di라고합니다.

직접 메모리 액세스가 가능한 포트 (Tour 3 DMA 병렬 포트)는 PS / 2 모델 57, 90, 95에서 사용되었습니다. 프린터로 출력 할 때 처리량을 늘리고 프로세서를 오프로드하기 위해 도입되었습니다. 포트로 작업하는 프로그램은 메모리에 출력 할 데이터 블록을 설정하기 만하면되며 Centronics 프로토콜을 통한 출력은 프로세서의 참여없이 수행되었습니다.

나중에 Centronics 하드웨어 기반 교환 프로토콜 인 Fast Centronics를 구현하는 다른 LPT 포트 어댑터가 나타났습니다. 그들 중 일부는 FIFO 데이터 버퍼-병렬 포트 FIFO 모드를 사용했습니다. 표준화되지 않은 다른 제조업체의 이러한 포트에는 자체 특수 드라이버가 필요했습니다. 표준 포트 레지스터를 직접 제어하는 \u200b\u200b프로그램은 추가 기능을 사용할 수 없습니다. 이 포트는 종종 VLB 멀티 카드의 일부입니다. ISA 버스에는 옵션이 있으며 시스템 보드에 통합되어 있습니다.

1.3. IEEE 1284 표준

1994 년에 채택 된 IEEE 1284 병렬 인터페이스 표준은 SPP, EPP 및 ECP 포트를 설명합니다. 표준은 5 가지 데이터 교환 모드, 모드 매칭 방법, 물리적 및 전기적 인터페이스를 정의합니다. IEEE 1284에 따르면 병렬 포트를 통한 다음과 같은 통신 모드가 가능합니다.

♦ 호환 모드-Centronics 프로토콜을 사용한 단방향 (출력). 이 모드는 SPP 포트에 해당합니다.

♦ Nibble Mode (Nibble 모드) — 수신 할 상태 줄을 사용하여 2주기 (각 4 비트)로 바이트를 입력합니다. 이 교환 모드는 표준 포트의 기능 만 사용하므로 모든 어댑터에 적합합니다.

♦ 바이트 모드-수신 할 데이터 라인을 사용하여 전체 바이트를 입력하십시오. 이 모드는 출력 데이터를 읽을 수있는 포트에서만 작동합니다 (양방향 또는 PS / 2 투어 1, 위 참조).

♦ EPP 모드-양방향 통신 (EPP는 Enhanced Parallel Port를 나타냄). 인터페이스 제어 신호는 포트에 액세스하는주기 동안 하드웨어에 의해 생성됩니다. 외부 메모리 장치 및 LAN 어댑터로 작업 할 때 효과적입니다.

♦ ECP 모드 (ECP 모드)-RLE (Run Length Encoding) 방법 및 FIFO 버퍼 및 DMA (ECP는 확장 기능 포트)를 사용하여 하드웨어 데이터 압축이 가능한 양방향 데이터 교환. 인터페이스 제어 신호는 하드웨어에 의해 생성됩니다. 프린터 및 스캐너 (여기에서 압축을 사용할 수 있음) 및 다양한 블록 교환 장치에 효과적입니다.

표준은 소프트웨어가 호스트 (PC)와 주변 장치 (또는 연결된 두 번째 컴퓨터) 모두에서 사용 가능한 모드를 결정할 수있는 방법을 정의합니다. Centronics 하드웨어 프로토콜 (고속 Centronics, 병렬 포트 FIFO 모드)을 구현하는 비표준 포트 모드는 EPP 및 ECP 기능이 있음에도 불구하고 IEEE 1284 모드가 아닐 수 있습니다.

시스템 보드에 LPT 포트가있는 컴퓨터의 경우 모드 (SPP, EPP, ECP 또는 이들의 조합)는 BIOS 설정에서 설정됩니다. 호환성 모드는 SPP 포트와 완전히 일치합니다. 나머지 모드는 아래에서 자세히 설명합니다.

교환 모드를 설명 할 때 다음 개념이 나타납니다.

♦ 호스트-병렬 포트가있는 컴퓨터;

♦ PU-이 포트에 연결된 주변 장치;

♦ Ptr-신호 이름에서 전송 PU를 나타냅니다.

♦ 직접 채널-호스트에서 제어실로 데이터를 출력하기위한 채널.

♦ 역방향 채널-제어실에서 호스트로 데이터를 입력하기위한 채널.

1.3.1. 니블 모드-니블 모드

니블 모드는 양방향 교환을 위해 설계되었으며 모든 표준 포트에서 작동 할 수 있습니다. 포트에는 5 개의 상태 입력 라인이 있으며,이를 통해 제어판은 4 단계를 호스트 바이트 (니블-니블, 4 비트)에 2 단계로 전송할 수 있습니다. 이 모드에서 사용할 수있는 인터럽트를 발생시키는 Ack # 신호는 상태 레지스터의 비트 6에 해당하며 바이트를 조립할 때 비트의 소프트웨어 조작을 복잡하게합니다. 포트 신호는 표에 나와 있습니다. 1.2, 시간 다이어그램-그림. 1.1.

표 1.2. 니블 입력 모드의 LPT 포트 신호

| 연락 | SPP 신호 | I / O | 비트 | 설명 |

| 14 | 자동 공급 번호 | 오 | CR.1 | HostBusy-승인 신호. 레벨이 낮 으면 사 중음 수신 준비 상태를, 높음은 사 중음 수신 상태를 확인합니다 |

| 17 | #에서 선택 | 오 | CR.3 | |

| 10 | 승인 번호 | 나 | SR.6 | PtrClk. 낮음은 노트북의 준비 상태를 나타내고 높음은 HostBusy 신호에 대한 응답을 나타냅니다. |

| 11 | 바쁜 | 나 | SR.7 | 데이터 비트 3을 수신 한 다음 비트 7을 수신 |

| 12 | 다시 | 나 | Sr.5 | 데이터 비트 2를 수신 한 다음 비트 6을 수신 |

| 13 | 선택 | 나 | SR.4 | 데이터 비트 1을 수신 한 다음 비트 5를 수신 |

| 15 | 오류 # | 나 | SR.3 | 데이터 비트 0을 수신 한 다음 비트 4를 수신 |

그림. 1.1. 니블 모드에서 데이터 수신

니블 모드에서 데이터 바이트를 수신하는 단계는 다음과 같습니다.

2. PU는 응답으로 노트북을 입력 상태 표시 줄에 놓습니다.

3. PU는 PtrClk 라인에서 낮은 레벨을 설정하여 노트북의 준비 상태를 알립니다.

4. 호스트는 HostBusy 라인에서 상위 레벨을 설정하여 노트북 수신 및 처리 중임을 나타냅니다.

6. 두 번째 노트북에 대해 1-5 단계를 반복합니다.

1/2 바이트 모드는 프로세서를 많이로드하므로 환율을 50Kb / s 이상으로 올릴 수 없습니다. 무조건적인 장점은 모든 포트에서 작동한다는 것입니다. 데이터 흐름이 적은 경우 (예 : 프린터와의 통신)에 사용됩니다. 그러나 LAN 어댑터, 외부 디스크 드라이브 및 CD-ROM과 통신 할 때 많은 양의 데이터를 수신하려면 사용자 측에서 많은 인내심이 필요합니다.

1.3.2. 양방향 바이트 모드-바이트 모드

이 모드에서는 CR.5 \u003d 1 비트를 설정하여 출력 데이터 버퍼를 비활성화 할 수있는 양방향 포트를 사용하여 데이터를 수신합니다. 이전과 마찬가지로 모드는 프로그램으로 제어됩니다-모든 승인 신호는 드라이버에 의해 분석되고 설정됩니다. 포트 신호는 표에 설명되어 있습니다. 1.3, 시간 다이어그램-그림. 1.2.

표 1.3. 바이트 I / O의 LPT 포트 신호

| 연락 | SPP 신호 | 바이트 모드의 이름 | I / O | 비트 | 설명 |

| 1 | 스트로브 # | Hostclk | 오 | CR.0 | 펄스 (낮은 레벨)는 각 사이클의 끝에서 바이트의 수신을 확인합니다 |

| 14 | 자동 공급 번호 | 호스트 버스 | 아 | CR.1 | 승인 신호. 낮은 수준은 호스트가 바이트를 수락 할 의사가 있음을 의미합니다. 높은 수준은 바이트 수신으로 설정됩니다 |

| 17 | #에서 선택 | 활성 | 아 | CR.3 | 높음은 IEEE 1284 모드에서 교환을 나타냅니다 (SPP 모드에서는 낮음) |

| 16 | 초기화 # | 초기화 # | 오 | CR.2 | 사용되지 않습니다. 높게 설정 |

| 10 | 승인 번호 | Ptrclk | 나 | SR.6 | 데이터 라인에서 데이터의 유효성을 나타내려면 낮음으로 설정하십시오. HostBusy 신호에 대한 응답으로 낮음으로 설정 |

| 11 | 바쁜 | 프트 르뷔시 | 나 | SR.7 | 순방향 채널 사용 중 상태 |

| 12 | PE | AckDataReq¹ | 나 | Sr.5 | |

| 13 | 선택 | Xflag¹ | 나 | SR.4 | 확장 성 플래그 |

| 15 | 오류 # | DataAvail # ¹ | 나 | SR.3 | 역방향 전송 채널이 있음을 나타내는 제어판이 설치되어 있습니다. |

| 2-9 | 자료 | 자료 | I / O | DR | 양방향 (정방향 및 역방향) 데이터 채널 |

그림. 1.2. 바이트 모드에서 데이터 수신

데이터 바이트 수신 단계는 다음과 같습니다.

1. 호스트는 HostBusy 라인에서 낮은 레벨을 설정하여 데이터를 수신 할 준비가되었음을 나타냅니다.

2. 응답으로 컨트롤은 데이터 라인에 데이터 바이트를 배치합니다.

3. 제어판은 PtrClk 라인에서 낮은 레벨을 설정하여 바이트의 유효성을 알립니다.

4. 호스트는 HostBusy 행에서 상위 레벨을 설정하여 바이트 수신 및 처리 중임을 나타냅니다.

5. PtrClk 라인에서 하이 레벨을 설정하여 제어판이 응답합니다.

6. 호스트는 HostClk 펄스로 바이트 수신을 확인합니다.

1-6 단계는 이후의 각 바이트에 대해 반복됩니다. 승인은 한 쌍의 HostBusy 및 PtrClk 신호에 의해 수행됩니다. 제어판은 HostClk 신호를 사용하지 않을 수 있습니다 (Centronics 인터페이스의 Ack # 신호를 연상시키는 다음 바이트를 발행하라는 초대입니다). 바이트 모드를 사용하면 표준 모드에서 역방향 채널 속도를 순방향 채널 속도로 올릴 수 있습니다. 그러나 저사양 PS / 2 시스템에서 주로 사용하던 양방향 포트에서만 작동 할 수 있지만 거의 모든 최신 포트는 양방향 모드 (BIOS 설정, Bi-Di 또는 PS / 2에서)로 구성 할 수 있습니다.

1.3.3. EPP 모드

EPP (Enhanced Parallel Port-Enhanced Parallel Port) 프로토콜은 IEEE 1284 표준을 채택하기 오래 전에 Intel, Xircom 및 Zenith Data Systems에서 개발 한 것으로,이 프로토콜은 병렬 포트 통신 성능을 향상 시키도록 설계되었으며 인텔 386SL 칩셋 (칩 82360)에서 처음 구현되었습니다. 이후 많은 회사에서 추가 병렬 포트 프로토콜로 채택했습니다. IEEE 1284를 채택하기 전에 구현 된 프로토콜 버전은 현재 표준과 다릅니다 (아래 참조).

EPP는 4 가지 유형의 교환주기를 제공합니다.

♦ 데이터 기록;

♦ 데이터 읽기;

♦ 주소 기록;

♦ 주소를 읽습니다.

데이터주기를 쓰고 읽는 목적은 분명합니다. 주소주기는 주소, 채널 및 제어 정보를 전송하는 데 사용됩니다. 통신주기는 적용된 스트로브 신호에 의한 주소주기와 다릅니다. EPP 포트 신호의 목적과 SPP 신호와의 관계는 표에 설명되어 있습니다. 1.4.

표 1.4. EPP I / O의 LPT 포트 신호

| 연락 | SPP 신호 | EPP 이름 | I / O | 설명 |

| 1 | 스트로브 # | 쓰기 # | 오 | 낮은 쓰기주기, 높은 읽기주기 |

| 14 | AutoLF # | DataStb # | 오 | 데이터 스트로브. 데이터주기에서 낮은 수준으로 설정 |

| 17 | #에서 선택 | AddrStb # | 오 | 스트로브 주소. 주소주기에서 낮은 수준으로 설정 |

| 16 | 초기화 # | 재설정 # | 오 | PU 리셋 (낮음) |

| 10 | 승인 번호 | INTR # | 나 | PU 중단 |

| 11 | 바쁜 | 기다림 # | 나 | 승인 신호. 로우 레벨은 사이클 시작 (스트로브를 로우 레벨로 설정), 하이로 전환-사이클 완료 (스트로브 제거)를 허용합니다. |

| 2-9 | 자료 | 광고 | I / O | 양방향 주소 / 데이터 버스 |

| 12 | 페이퍼 엔드 | AckDataReq¹ | 나 | |

| 13 | 선택 | Xflag¹ | 나 | 주변기기 개발자의 판단에 따라 사용 |

| 15 | 오류 # | DataAvail # ¹ | 나 | 주변기기 개발자의 판단에 따라 사용 |

¹ 신호가 일치하는 순서대로 작동합니다 (아래 참조).

EPP 포트에는 확장 레지스터 세트 (표 1.5)가 있으며, I / O 공간에서 5-8 개의 인접 바이트를 차지합니다.

표 1.5. EPP 포트 레지스터

| 등록 이름 | 오프셋 | 모드 | R / 승 | 설명 |

| SPP 데이터 포트 | +0 | SPP / EPP | 여 | SPP 데이터 레지스터 |

| SPP 상태 포트 | +1 | SPP / EPP | R | SPP 상태 레지스터 |

| SPP 제어 포트 | +2 | SPP / EPP | 여 | SPP 관리 등록 |

| EPP 주소 포트 | +3 | EPP | R / 승 | EPP 주소 레지스터. 읽거나 쓰면 EPP 주소를 읽거나 쓰는 관련주기가 생성됩니다. |

| EPP 데이터 포트 | +4 | EPP | R / 승 | EPP 데이터 레지스터. 읽기 (쓰기)는 EPP 데이터 읽기 (쓰기) 관련주기를 생성합니다. |

| 미정 | +5…+7 | EPP | N / a | 일부 컨트롤러는 16-32 비트 I / O 작업에 사용할 수 있습니다. |

위에서 설명한 프로그램 제어 모드와 달리, 각 교환주기에 대한 외부 EPP 포트 신호는 포트 레지스터에서 하나의 쓰기 또는 읽기 작업을 위해 하드웨어에 의해 형성됩니다. 그림. 1.3은 프로세서 시스템 버스의 기록주기에 내장 된 외부 교환주기를 나타내는 데이터 기록주기의 다이어그램이다 (때때로이주기를 연결이라고 함). 쓰기 주소주기는 외부 인터페이스의 스트로브에서만 데이터주기와 다릅니다.

그림. 1.3. EPP 데이터 기록주기

데이터 기록주기는 다음 단계로 구성됩니다.

1. 프로그램은 포트 4 (EPP 데이터 포트)에 대한 출력주기 (IOWR #)를 수행합니다.

2. 어댑터는 Write # 신호 (low)를 설정하고 데이터는 LPT 포트의 출력 버스에 배치됩니다.

3. Wait #이 낮 으면 데이터 스트로브가 설정됩니다.

4. 포트가 PU로부터의 확인을 기다리고 있습니다 (대기 #을 상위 레벨로 전송하십시오).

5. 데이터 스트로브가 제거되고 외부 EPP주기가 종료됩니다.

6. 출력 프로세서 사이클이 종료됩니다.

7. PU는 대기 #를 낮게 설정하여 다음 사이클이 시작될 가능성을 나타냅니다.

어드레스 판독주기의 예가도 1에 도시되어있다. 1.4. 데이터 판독주기는 다른 게이트 신호를 사용할 때만 다릅니다.

그림. 1.4. EPP 읽기 주소주기

EPP의 주요 특징은 하나의 프로세서 입력 / 출력주기 동안 외부 전송을 구현하는 것입니다. 이를 통해 높은 환율 (0.5–2MB / s)을 달성 할 수 있습니다. EPP 병렬 포트에 연결된 제어판은 ISA 슬롯을 통해 연결된 장치의 속도로 작동 할 수 있습니다.

당연히, 제어판은 버스 교환주기에서 프로세서를 "일시 정지"해서는 안됩니다. 이를 통해 PC 시간 제한 메커니즘을 보장하여 15 마이크로 초 이상 지속되는 모든 교환주기를 강제 종료합니다. 많은 EPP 구현에서 어댑터 자체는 인터페이스 시간 초과를 모니터링합니다. 제어 장치가 특정 시간 (5 μs) 동안 응답하지 않으면 사이클이 중지되고 추가 (표준화되지 않은) 어댑터 상태 레지스터에 오류가 기록됩니다.

IEEE 1284를 채택하기 전에 개발 된 EPP 장치는 사이클 시작에서 다릅니다. DataStb # 또는 AddrStb # 스트로브는 WAIT #의 상태에 관계없이 설정됩니다. 즉, PU는 다음 사이클의 시작을 지연시킬 수 없습니다 (필요한 시간으로 늘릴 수는 있음). 이 사양을 EPP 1.7 (Xircom에서 제안)이라고합니다. IEEE 1284 EPP와 호환되는 주변 장치는 EPP 1.7 컨트롤러와 정상적으로 작동하지만 EPP 1.7 표준의 PU는 EPP 1284 컨트롤러와 작동하지 않을 수 있습니다.

소프트웨어 관점에서 EPP 포트 컨트롤러는 단순 해 보입니다 (표 1.5 참조). 두 개의 레지스터 (EPP 주소 포트 및 EPP 데이터 포트)가 포트의 기본 주소에 대해 0, 1 및 2의 오프셋으로 표준 포트의 3 개 레지스터에 추가되어 읽기 및 쓰기가 관련 외부 루프를 생성합니다.

표준 포트 레지스터의 목적은 소프트웨어 제어 교환을 사용하도록 설계된 제어판 및 소프트웨어와 EPP 포트의 호환성을 위해 저장되었습니다. 수신 확인 신호는 하드웨어에서 어댑터에 의해 생성되므로 CR 제어 레지스터에 쓸 때 신호 Strobe #, AutoFeed # 및 SelectIn #에 해당하는 비트 0, 1 및 3은 0 값을 가져야합니다. 소프트웨어 개입으로 승인 시퀀스가 \u200b\u200b중단 될 수 있습니다. 일부 어댑터에는 특수 보안 기능 (EPP Protect)이 있으며이 기능을 사용하면 이러한 비트의 소프트웨어 수정이 차단됩니다.

EPP 데이터 레지스터를 사용하면 단일 REP INSB 또는 REP OUTSB 명령으로 데이터 블록을 전송할 수 있습니다. 일부 어댑터는 EPP 데이터 레지스터에 16/32 비트 액세스를 허용합니다. 이 경우 어댑터는 단순히 EPP 데이터 레지스터의 주소로 4-7 범위의 오프셋으로 주소를 해독하지만 프로세서는 8 비트를보고합니다. 그런 다음 EPP 데이터 레지스터 주소에 대한 16 비트 또는 32 비트 액세스는 오프셋 4에서 시작하는 증분 주소에서 2 개 또는 4 개의 버스주기를 자동으로 생성합니다. 이러한주기는 동일한 수의 단일주기보다 빠르게 실행됩니다. EPP 데이터 레지스터 주소보고를위한 더 많은 "고급"어댑터는 32 비트 및 최대 4 바이트까지 한 프로세서 주기로 전송할 수 있습니다. 이는 LAN 어댑터, 외장 드라이브, 테이프 드라이브 및 CD-ROM에 충분한 최대 2MB / s의 성능을 보장합니다. EPP 주소 루프는 항상 단일 바이트 모드에서만 실행됩니다.

EPP의 중요한 기능은 프로세서가 제어판에 실시간으로 액세스한다는 것입니다. 버퍼링은 없습니다. 드라이버는 정확히 알려진 시점에서 상태를 모니터링하고 명령을 실행할 수 있습니다. 읽기 및 쓰기주기는 임의 순서로 번갈아 가거나 블록 단위로 진행될 수 있습니다. 이러한 유형의 교환은 레지스터 지향 컨트롤러 또는 실시간으로 작동하는 컨트롤러 (예 : 정보 수집 및 제어 장치)에 편리합니다. 이 모드는 저장 장치, 네트워크 어댑터, 프린터, 스캐너 등에 적합합니다.

불행히도 EPP 모드가 모든 포트에서 지원되는 것은 아닙니다. 예를 들어 여러 노트북 PC에는 없습니다. 따라서 컴퓨터와의 호환성을 높이기 위해 자체 장치를 개발할 때는 ECP 모드에 중점을 두어야합니다.

1.3.4. ECP 모드

Hewlett Packard 및 Microsoft는 ECP 프로토콜 (확장 기능 포트)을 제안하여 프린터 또는 스캐너와 같은 컨트롤러와 통신합니다. EPP와 마찬가지로이 프로토콜은 컨트롤러와 고성능 양방향 호스트 데이터 교환을 제공합니다.

양방향의 ECP는 두 가지 유형의주기를 제공합니다.

♦ 데이터 쓰기 및 읽기주기;

♦ 쓰기 및 읽기 명령주기.

명령주기는 채널 주소 전송과 RLC 카운터 전송 (Run-Length Count)의 두 가지 유형으로 나뉩니다.

EPP와는 달리, ECP 프로토콜과 함께 어댑터의 소프트웨어 (등록) 모델 표준이 즉시 나타 났으며 이는 Microsoft의 IEEE 1284 확장 기능 포트 프로토콜 및 ISA 인터페이스 표준에 설명되어 있습니다. 이 문서는 IEEE 1284 표준에 의해 지정되지 않은 프로토콜 속성을 정의합니다.

RLE 방법에 따라 호스트 어댑터에 의한 데이터 압축;

순방향 및 역방향 채널을위한 FIFO 버퍼링;

♦ DMA 및 소프트웨어 입출력의 적용.

RLE (Run-Length Encoding) 방법을 사용하는 실시간 압축을 사용하면 긴 바이트의 반복 바이트가있는 래스터 이미지를 전송할 때 64 : 1 압축비를 얻을 수 있습니다. 압축은 호스트와 PU가 모두 지원하는 경우에만 사용할 수 있습니다.

채널 ECP는 하나의 물리적 장치의 일부인 많은 논리적 장치를 처리하는 데 사용됩니다. 예를 들어 하나의 병렬 포트에만 연결된 팩스 / 프린터 / 모뎀 장치의 경우 팩스를 받고 프린터로 인쇄 할 수 있습니다. SPP 모드에서 프린터가 통화 중 신호를 설정하면 프린터가 신호를 수신 할 때까지 채널이 데이터로 통화 중입니다. ECP 모드에서 소프트웨어 드라이버는 단순히 동일한 포트에서 다른 논리 채널을 처리합니다.

ECP 프로토콜은 SPP 신호보다 우선합니다 (표 1.6).

표 1.6. ECP I / O의 LPT 포트 신호

| 연락 | SPP 신호 | ECP의 이름 | I / O | 설명 |

| 1 | 스트로브 # | Hostclk | 아 | 순방향 전송 (출력)을 위해 PeriphAck와 페어링 된 데이터 스트로브 |

| 14 | AutoLF # | Hostack | 아 | 순방향으로 전송할 때 사이클 유형 (명령 / 데이터)을 나타냅니다. 반대 방향으로 전송하기 위해 PeriphClk와 페어링 된 확인 신호로 사용 |

| 17 | #에서 선택 | 활성 | 오 | 높음은 IEEE 1284 모드에서 교환을 나타냅니다 (SPP 모드에서는 낮음) |

| 16 | 초기화 # | ReverseRequest # | 오 | 반대 요청. 레벨이 낮 으면 채널이 반전됨을 나타냅니다. |

| 10 | 승인 번호 | 페리 ip 크 | 나 | 뒤로 전송하기 위해 HostAck와 쌍을 이루는 데이터 스트로브 |

| 11 | 바쁜 | 페리 핵 | 나 | 순방향 전송을 위해 HostClk와 페어링 된 확인 신호로 사용됩니다. 형상 방향으로 전송할 때 형식 명령 / 데이터를 나타냅니다. |

| 12 | 페이퍼 엔드 | AckReverse # | 나 | 역 확인. ReverseRequest #에 대한 응답으로 low로 번역 |

| 13 | 선택 | Xflag¹ | 나 | 확장 성 플래그 |

| 15 | 오류 # | PeriphRequest # ¹ | 나 | 역방향 전송 채널의 가용성 (가용성)을 나타내는 제어판이 설치되어 있습니다 ¹ |

| 2-9 | 자료 | 자료 | I / O | 양방향 데이터 채널 |

¹ 신호가 일치하는 순서대로 작동합니다 (아래 참조).

ECP 어댑터는 하드웨어에서 외부 승인 프로토콜 신호도 생성하지만 작동은 EPP 모드와 크게 다릅니다.

그림. 1.5, 그리고 직접 전송의 두 사이클의 다이어그램이 표시됩니다. 데이터 사이클 다음에 명령 사이클이 이어집니다. 사이클 유형은 HostAck 라인의 레벨에 의해 설정됩니다. 데이터 사이클이 높고 명령 사이클이 낮습니다. 명령 루프에서 바이트는 채널 주소 또는 RLE 카운터를 포함 할 수 있습니다. 독특한 기능은 비트 7 (높음)입니다. 0 인 경우 비트 0–6에는 RLE 카운터 (0–127)가 포함됩니다 (채널 주소 인 경우). 그림. 1.5, b는 한 쌍의 피드백 사이클을 보여준다.

그림. 1.5. ECP 모드에서의 전송 : a-앞으로, b-뒤로

EPP 교환 다이어그램과 달리, 그림. 프로세서 시스템 버스주기의 1.5 신호는 표시되지 않습니다. 이 모드에서 PU와의 프로그램 교환은 FIFO 버퍼를 통해 연결된 두 개의 상대적으로 독립적 인 프로세스로 나뉩니다. 드라이버는 DMA 또는 소프트웨어 I / O를 사용하여 FIFO 버퍼와 교환 할 수 있습니다. 버퍼와 PU의 교환은 하드웨어 ECP 어댑터에 의해 수행됩니다. ECP 모드의 드라이버에는 정확한 교환 프로세스 상태에 대한 정보가 없지만 일반적으로 완료 여부에 관계없이 중요합니다.

외부 인터페이스에서 직접 데이터 전송은 다음 단계로 구성됩니다.

1. 호스트는 데이터를 채널 버스에 배치하고 HostAck 라인에서 데이터주기 부호 (높은 수준) 또는 명령 (낮은 수준)을 설정합니다.

2. 호스트는 HostClk 행에서 낮은 수준을 설정하여 데이터의 유효성을 나타냅니다.

3. PU는 PeriphAck 라인의 고급 설치로 응답합니다.

4. 호스트는 HostLCk 라인을 높은 수준으로 설정하며이 차이를 사용하여 제어판에 데이터를 기록 할 수 있습니다.

5. 제어판은 PeriphAck 라인에 낮은 레벨을 설정하여 다음 바이트를 수신 할 준비가되었음을 나타냅니다.

ECP 로의 전송은 인터페이스의 양쪽에 존재할 수있는 FIFO 버퍼를 통해 발생하므로 데이터가 전송되는 것으로 간주 할 수있는 단계를 이해하는 것이 중요합니다. HostClk 회선이 높아지면 4 단계에서 데이터가 전송 된 것으로 간주됩니다. 이때 송수신 바이트의 카운터가 수정됩니다. ECP 프로토콜에는 3 단계와 4 단계 사이의 교환을 방해하는 조건이 있습니다. 그러면이 데이터를 전송 된 것으로 간주해서는 안됩니다.

그림에서 1.5는 ECP와 EPP의 또 다른 차이점을 보여줍니다. EPP를 통해 운전자는 방향 변경을 확인할 필요없이 순방향 및 역방향 전송주기를 교대로 전환 할 수 있습니다. ECP에서 방향 변경에 동의해야합니다. 호스트는 ReverseRequest #을 설정하여 역방향을 요청한 후 AckReverse # 신호의 확인을 기다려야합니다. 이전 사이클은 직접 액세스를 통해 수행 될 수 있으므로, 드라이버는 직접 액세스가 완료 될 때까지 기다리거나 중단하고, FIFO 버퍼를 언로드하고, 전송 된 바이트 카운터의 정확한 값을 결정한 다음 역순으로 요청해야합니다.

포스트 백은 다음 단계로 구성됩니다.

1. 호스트가 채널 방향 변경을 요청하여 ReverseRequest # 라인에서 낮은 레벨을 설정합니다.

2. 제어 장치는 AckReverse # 라인에서 로우 레벨을 설정하여 방향 변경을 허용합니다.

3. 컨트롤러는 데이터를 채널 버스에 놓고 PeriphAck 라인에서 데이터 사이클 (높은 레벨) 또는 명령 (낮은 레벨)의 부호를 설정합니다.

4. PU는 데이터의 유효성을 나타내는 PeriphClk 줄에 낮은 수준을 설정합니다.

5. 호스트는 HostAck 라인에서 고급 설치로 응답합니다.

6. PU는 PeriphClk 라인의 높은 수준을 설정합니다. 이 차이는 호스트별로 데이터를 기록하는 데 사용할 수 있습니다.

7. 호스트는 HostAck 라인에서 하위 레벨을 설정하여 다음 바이트를 수신 할 준비가되었음을 나타냅니다.

1.3.5. ECP 포트 모드 및 레지스터

IEEE 1284 어댑터 용 소프트웨어 인터페이스 및 ECP 레지스터는 Microsoft 사양에 의해 정의됩니다. ECP 포트는 표에 표시된 다양한 모드에서 작동 할 수 있습니다. 1.7, 여기서 코드는 ECR 레지스터의 모드 필드 (비트)에 해당합니다.

표 1.7. ECP 포트 모드

| 코드 | 모드 |

| 000 | SPP 모드, 표준 (전통) 모드 |

| 001 | 양방향 모드, 양방향 포트 (PS / 2의 경우 유형 1) |

| 010 | FIFO 및 DMA를 사용하는 고속 Centronics 단방향 |

| 011 | ECP 병렬 포트 모드, 실제 ECP 모드 |

| 100 | EPP 병렬 포트 모드, EPP¹ 모드 |

| 101 | 예약 됨 |

| 110 | 테스트 모드, FIFO 작동 및 인터럽트 테스트 |

| 111 | 구성 모드, 구성 레지스터에 대한 액세스 |

¹이 모드는 Microsoft 사양의 일부가 아니지만 ECP + EPP 모드가 CMOS 설정에서 설정된 경우 많은 포트 어댑터에서 EPP로 처리됩니다.

ECP 어댑터의 레지스터 모델 (표 1.8)은 표준 버스 아키텍처 및 ISA 어댑터의 속성을 사용합니다. 여기서 10 개의 하위 주소 버스 라인 만 I / O 포트 주소를 해독하는 데 사용됩니다. 따라서 예를 들어, 포트, 포트 + 400h, 포트 + 800h ... 주소에 대한 호출은 0-3FFh 범위에있는 포트 주소에 대한 호출로 인식됩니다. 최신 PC 및 어댑터는 더 많은 수의 주소 비트를 디코딩하므로 주소 0378h 및 0778H에 대한 호출은 두 개의 다른 레지스터로 처리됩니다. 표준 포트 레지스터 (오프셋 400-402Н)의 "뒤에"추가 ECR 레지스터를 배치하는 데는 두 가지 목표가 있습니다. 첫째, 이러한 주소는 기존 어댑터 및 해당 드라이버에서 사용한 적이 없으며 ECP에서의 사용으로 인해 사용 가능한 I / O 주소 공간이 좁아지지는 않습니다. 둘째, 이는 000-001 모드에서 이전 어댑터와의 호환성을 보장하고 확장 레지스터에 액세스하여 ECP 어댑터의 존재를 판별 할 가능성을 보장합니다.

표 1.8. ECP 레지스터

| 오프셋 | 이름 | R / 승 | ECP 모드 ¹ | 직함 |

| 000 | DR | R / 승 | 000-001 | 데이터 레지스터 |

| 000 | ECPAFIFO | R / 승 | 011 | ECP 주소 FIFO |

| 001 | Sr | R / 승 | 모두 | 상태 등록 |

| 002 | CR | R / 승 | 모두 | 제어 레지스터 |

| 400 | SDFIFO | R / 승 | 010 | 병렬 포트 데이터 FIFO |

| 400 | ECPDFIFO | R / 승 | 011 | ECP 데이터 FIFO |

| 400 | TFIFO | R / 승 | 110 | fifo 테스트 |

| 400 | ECPCFGA | R | 111 | 구성 레지스터 A |

| 401 | ECPCFGB | R / 승 | 111 | 구성 레지스터 B |

| 402 | ECR | R / 승 | 모두 | 확장 된 제어 레지스터 |

¹ 레지스터는이 모드에서만 사용할 수 있습니다 (ECR 레지스터의 비트 7-5 값이 표시됨)

각 ECP 모드에는 자체 기능 레지스터가 있으며 사용할 수 있습니다. 스위칭 모드는 ECR 레지스터에 기록하여 수행됩니다. 기본적으로 활성화 된 "대기"모드는 000 또는 001입니다. 이들 중 하나에서 1/2 바이트 입력 모드가 작동합니다. 이러한 모드에서 항상 다른 모드로 전환 할 수 있지만 이전 모드 (010–111)에서는 000 또는 001로만 전환 할 수 있습니다. 인터페이스가 올바르게 작동하려면 이전 모드를 종료하기 전에 직접 액세스 교환이 완료되고 FIFO 버퍼가 지워질 때까지 기다려야합니다.

000 (SPP) 모드에서 포트는 단방향 소프트웨어 제어 SPP 포트로 작동합니다.

모드 001 (Bi-Di PS / 2)에서 포트는 1 PS / 2 유형의 양방향 포트로 작동합니다. 모드 000에서는 비트 CR.5에서 데이터 채널을 반전시킬 가능성이 다릅니다.

010 모드 (Fast Centronics)는 DMA를 사용하는 FIFO 버퍼를 통한 고성능 출력 전용입니다. Centronics 핸드 셰이크는 하드웨어에 의해 생성됩니다. 인터럽트 요청 신호는 신호 Ack #가 아닌 FIFO 버퍼 상태에 의해 생성됩니다 (단일 바이트에 대한 요청은 고속 블록 출력 드라이버에 관심이 없습니다).

모드 011은 위에서 설명한 실제 ECP 모드입니다. 컨트롤러로 전송되는 데이터 및 명령의 흐름은 각각 ECPDFIFO 및 ECPAFIFO 레지스터를 통해 FIFO 버퍼에 배치됩니다. FIFO에서 루프의 해당 부호 (HostAck 라인 상태)로 추론됩니다. PU로부터 수신 된 데이터 스트림은 ECPDFIFO 레지스터를 통해 FIFO 버퍼로부터 추출된다. PU에서 명령주기의 주소를 얻는 것은 제공되지 않습니다. ECPDFIFO 레지스터와의 교환은 DMA 채널을 통해서도 이루어질 수 있습니다.

전송 중 RLE 압축은 프로그래밍 방식으로 수행됩니다. 행에서 두 개 이상의 동일한 바이트의 데이터를 전송하기 위해 ECPAFIFO 레지스터에 바이트가 기록되는데, 하위 7 비트에는 RLC 카운터가 포함되며 (RLC \u003d 127은 128 반복에 해당), 최상위 비트는 0입니다. 그런 다음 바이트 자체가 ECPDFIFO에 기록됩니다. PU는이 바이트 쌍 (명령 바이트 및 데이터 바이트)을 허용하여 압축 해제를 수행합니다. 제어 장치에서 스트림을 수신 할 때 ECP 어댑터는 하드웨어에서 압축 해제를 수행하고 이미 압축 해제 된 데이터를 FIFO 버퍼에 넣습니다. 이것으로부터 압축과 DMA를 동시에 사용하는 데이터 출력은 불가능하다는 것이 명백하다.

모드 100 (EPP)은 EPP 모드를 활성화하는 한 가지 방법입니다 (어댑터가 지원하고 CMOS 설정에서 활성화 된 경우).

모드 110 (테스트 모드)은 FIFO와 인터럽트의 상호 작용을 테스트하도록 설계되었습니다. DMA를 사용하거나 프로그래밍 방식으로 TFIFO 레지스터와 데이터를주고받을 수 있습니다. 교환은 외부 인터페이스에 영향을 미치지 않습니다. 어댑터는 승인 신호가 지연없이 도착하는 것처럼 최대 인터페이스 속도로 유휴 작업을 수행합니다. 어댑터는 버퍼 상태를 모니터하고 필요에 따라 인터럽트 요청 신호를 생성합니다. 따라서 프로그램은 채널의 최대 대역폭을 결정할 수 있습니다.

모드 111 (구성 모드)은 구성 레지스터에 액세스하기위한 것입니다. 모드를 강조 표시하면 교환 중에 어댑터 및 프로토콜이 올바르지 않은 구성 변경으로부터 보호됩니다.

이미 언급했듯이 각 ECP 모드에는 자체 기능 레지스터가 있습니다 (표 1.8).

DR 데이터 레지스터는 프로그램 제어 모드 (000 및 001)에서만 데이터 전송에 사용됩니다.

SR 상태 레지스터는 SPP에서와 같이 해당 라인의 신호 값을 전송합니다.

CR 제어 레지스터에는 SPP와 일치하는 비트 할당이 있습니다. 모드 010, 011에서 비트 0, 1 (AutoLF # 및 Strobe # 신호)에 쓰는 것은 무시됩니다.

ECPAFIFO 레지스터는 FIFO 버퍼에 명령 사이클 (비트 7에 따라 채널 주소 또는 RLE 카운터) 정보를 배치하는 데 사용됩니다. 버퍼의 정보는 출력 명령 루프에서 발행됩니다.

SDFIFO 레지스터는 010 모드에서 데이터를 전송하는 데 사용됩니다. 레지스터에 기록 된 (또는 DMA 채널을 통해 전송 된) 데이터는 Centronics 하드웨어 프로토콜을 사용하여 FIFO 버퍼를 통해 전송됩니다. 이 경우 전송의 전달 방향을 지정해야합니다 (비트 CR.5 \u003d 0).

DFIFO 레지스터는 011 모드 (ECP)에서의 데이터 교환에 사용됩니다. 레지스터에 쓰거나 읽은 데이터 (또는 DMA 채널을 통해 전송 된)는 ECP 프로토콜을 사용하여 FIFO 버퍼를 통해 전송됩니다.

TFIFO 레지스터는 110 모드에서 FIFO 버퍼를 테스트하기위한 메커니즘을 제공합니다.

ECPCFGA 레지스터를 사용하면 어댑터 정보 (식별 코드를 비트 단위)를 읽을 수 있습니다.

등록 ECPCFGB는 드라이버에 필요한 모든 정보를 저장합니다. 레지스터에 쓰는 것은 포트 작동에 영향을 미치지 않습니다.

ECR 레지스터는 ECP의 기본 관리 레지스터입니다. 비트의 목적은 다음과 같습니다.

♦ ECR-ECP MODE-ECP 모드를 설정합니다.

♦ ECR.4-ERRINTREN #-(Error Interrupt Disable)는 Error # 신호의 중단을 금지합니다 (음의 에지에서 비트 값이 0이면이 라인에 인터럽트 요청이 생성됨).

♦ ECR.3-DMAEN-(DMA Enable)은 DMA 채널에서의 교환을 허용합니다.

♦ ECR.2-SERVICEINTR-(서비스 인터럽트)는 DMA 사이클이 끝날 때 (활성화 된 경우), FIFO 버퍼 채우기 / 빈 임계 값 (DMA가 사용되지 않는 경우) 및 버퍼 오버 플로우 오류가 위 또는 아래에 발생하는 서비스 인터럽트를 금지합니다.

♦ ECR.1-FIFOFS-(FIFO Full Status) 버퍼가 가득 찼음을 나타냅니다. FIFOFS \u003d 1이면 버퍼에 사용 가능한 바이트가 없습니다.

♦ ECR.0-FIFOES-(FIFO Empty Status)는 완전한 빈 버퍼를 나타냅니다. FIFOFS \u003d FIFOES \u003d 1 조합은 FIFO 작업시 오류 (위 또는 아래에서 오버플로)를 의미합니다.

포트가 표준 또는 양방향 모드 (000 또는 001) 인 경우 처음 세 개의 레지스터는 표준 포트 레지스터와 정확히 동일합니다. 이렇게하면 이전 어댑터 및 새 어댑터가있는 이전 드라이버와의 드라이버 호환성이 보장됩니다.

프로그램과의 인터페이스에서 ECP 포트는 EPP와 유사합니다. 모드를 설정 한 후 (코드를 ECR 레지스터에 기록) 장치와의 데이터 교환은 해당 레지스터를 읽거나 쓰는 것으로 줄어 듭니다. FIFO 버퍼의 상태는 ECR 레지스터 또는 포트에서 서비스 인터럽트를 서비스하여 모니터링됩니다. 전체 승인 프로토콜은 하드웨어의 어댑터에 의해 생성됩니다. ECP 포트와의 데이터 교환 (명시 적 소프트웨어 제외)은 메모리 (DMA 채널)에 대한 직접 액세스를 통해 가능하며, 이는 큰 데이터 블록을 전송할 때 효과적입니다.

1.3.6. IEEE 1284 모드 협상

IEEE 1284 표준의 PU는 일반적으로 컨트롤러가이 표준에 의해 지정된 모든 모드를 구현할 것을 요구하지 않습니다. 특정 장치를 제어하는 \u200b\u200b모드와 방법을 결정하기 위해 표준은 협상 순서를 제공합니다. 이 시퀀스는 IEEE 1284를 지원하지 않는 구형 장치가 이에 응답하지 않고 컨트롤러가 표준 모드를 \u200b\u200b유지하도록 설계되었습니다. IEEE 1284 주변 장치는 해당 기능을보고 할 수 있으며 컨트롤러는 호스트와 PU를 모두 만족시키는 모드를 설정합니다.

협상 단계 동안 컨트롤러는 데이터 라인에 확장 성 바이트를 설정하여 인터페이스를 필수 모드로 설정하거나 제어판의 식별자를 수신 할 것인지를 확인합니다 (표 1.9). 식별자는 요청 된 모드 (EPP를 제외한 모든 리턴 채널 모드)에서 컨트롤러로 전송됩니다. 제어판은 Xflag 신호 (SPP 용어로 선택)를 사용하여 모든 IEEE 1284 장치에서 지원하는 하프 바이트를 제외하고 요청 된 역방향 채널 모드를 확인합니다. 확장 성 링크 요청 비트는 향후 표준 확장에서 추가 모드를 결정합니다.

표 1.9. 확장 성 바이트 비트

| 비트 | 설명 | 유효한 비트 조합 |

| 7 | 요청 확장 성 링크-예약 됨 | 1000 0000 |

| 6 | EPP 요청 | 0100 0000 |

| 5 | RLE를 통한 ECP 모드 요청 | 0011 0000 |

| 4 | RLE가없는 ECP 모드 요청 | 0001 0000 |

| 3 | 예약 됨 | 0000 1000 |

| 2 | 모드에서 응답이있는 장치 식별자 요청 : | |

| 니블 | 0000 0100 | |

| 바이트 | 0000 0101 | |

| RLE가없는 ECP | 0001 0100 | |

| RLE이 포함 된 ECP | 0011 0100 | |

| 1 | 예약 됨 | 0000 0010 |

| 0 | 니블 요청 | 0000 0001 |

| none | 바이트 모드 요청 | 0000 0000 |

조정 순서 (그림 1.6)는 다음 단계로 구성됩니다.

1. 호스트는 데이터 라인에 확장 성 바이트를 출력합니다.

2. 호스트는 신호를 SelectIn #으로 높게 설정하고 Low를 AutoFeed #으로 설정합니다. 이는 일치하는 시퀀스의 시작을 의미합니다.

3. 제어판은 Ack # (높음) 및 높음 (오류 번호, PaperEnd 및 선택)을 낮게 설정하여 응답합니다. 표준 1284를 "알지 못하는"장치는 대답을하지 않으며 추가 단계는 완료되지 않습니다.

4. 호스트는 확장 성 바이트를 제어 장치에 쓰도록 Strobe # 신호를 낮게 설정합니다.

5. 호스트는 높은 수준의 Strobe # 및 AutoLF # 신호를 설정합니다.

6. 제어판에 역방향 데이터 채널이있는 경우 PaperEnd 및 Error # 신호를 낮은 수준으로 설정하여 제어판이 응답합니다. 요청한 모드가 장치에서 지원되는 경우 선택 라인이 높게 (지원되지 않는 경우) 낮게 설정됩니다.

7. 제어판은 Ack # 라인에서 상위 레벨을 설정하여 일치 순서 완료를 표시 한 후 컨트롤러가 필요한 작동 모드를 설정합니다.

그림. 1.6. IEEE 1284 모드 협상 순서

1.3.7. 물리적 및 전기적 인터페이스

IEEE 1284 표준은 TTL과 레벨 호환되는 신호 수신기 및 송신기의 물리적 특성을 정의합니다. 표준 포트 사양에는 출력 회로의 유형, 부하 저항의 제한 값 및 회로 및 도체에 의해 도입 된 정전 용량이 지정되지 않았습니다. 비교적 낮은 환율에서, 이들 파라미터의 분산은 호환성 문제를 야기하지 않았다. 그러나 고급 (기능 및 전송 속도 측면) 모드에는 명확한 사양이 필요합니다. IEEE 1284는 두 가지 수준의 인터페이스 호환성을 정의합니다. 첫 번째 레벨 (레벨 I)은 속도는 느리지 만 데이터 전송 방향의 변경을 사용하는 장치에 대해 정의됩니다. 두 번째 레벨 (레벨 II)은 고속 및 긴 케이블을 사용하는 고급 모드에서 작동하는 장치에 대해 정의됩니다. 다음 요구 사항은 송신기에 적용됩니다.

♦ 부하가없는 신호 레벨은 -0.5 ... + 5.5V를 초과하지 않아야합니다.

♦ 14mA의 부하 전류에서 신호 레벨은 정전류에서 높은 레벨 (VOH)의 경우 + 2.4V보다 낮지 않아야하고 정전류에서 낮은 레벨 (VOL)의 경우 + 0.4V보다 높지 않아야합니다.

♦ 커넥터에서 측정 된 RO의 출력 임피던스는 VOH-VOL 레벨에서 50 ± 5 옴이어야합니다. 주어진 임피던스를 보장하기 위해 직렬 저항이 송신기의 출력 회로에 사용됩니다. 송신기와 케이블 임피던스가 일치하면 임펄스 노이즈가 줄어 듭니다.

♦ 펄스의 상승률은 0.05-0.4 V / ns 범위에 있어야합니다.

아래는 수신기 요구 사항입니다.

♦ 신호의 허용 가능한 최대 값 -2.0 ... + 7.0 V.

♦ 임계 값은 높을 경우 2.0V (VIH)보다 높지 않아야하고 낮을 경우 0.8V (VIL) 이상이어야합니다.

♦ 수신기는 0.2–1.2V 범위의 히스테리시스를 가져야합니다 (특별한 미세 회로-슈미트 트리거-히스테리시스).

♦ 미세 회로의 입력 전류 (유입 및 유출)는 20μA를 초과하지 않아야합니다. 입력 라인은 1.2kΩ 저항으로 + 5V 전원 버스에 연결됩니다.

♦ 입력 커패시턴스는 50 pF를 초과하지 않아야합니다.

ECP 사양이 나타 났을 때 Microsoft는 인터페이스의 각 줄에 동적 터미네이터를 사용하는 것이 좋습니다. 그러나 동적 터미네이터가 사용되지 않는 IEEE 1284 사양이 현재 준수되고 있습니다. 권장 입력, 출력 및 양방향 회로는 그림 4에 나와 있습니다. 1.7.

그림. 1.7. IEEE 1284 인터페이스 라인의 터미널 회로 : a-단방향 라인, b-양방향

IEEE 1284 표준은 사용되는 세 가지 유형의 커넥터를 정의합니다. 유형 A (DB-25) 및 B (Centronics-36)는 기존의 프린터 케이블, 유형 C-새로운 소형 36 핀 커넥터의 전형입니다.

기존 인터페이스 케이블에는 GND 회로 도체의 수에 따라 18 ~ 25 개의 전선이 있습니다. 이 도체는 서로 꼬이거나 꼬이지 않을 수 있습니다. 케이블 차폐에 대한 엄격한 요구 사항은 없었습니다. 이러한 케이블은 2MB / s의 전송 속도와 2m 이상의 길이에서 안정적으로 작동하지 않을 수 있습니다.

IEEE 1284 표준은 케이블 속성을 관리합니다.

♦ 모든 신호 라인은 별도의 리턴 (공통) 와이어로 상호 연결되어야합니다.

♦ 각 쌍의 주파수는 4-16 MHz의 주파수 범위에서 62 ± 6 Ohms의 임피던스를 가져야합니다.

♦ 쌍 사이의 누화 수준이 10 %를 초과하지 않아야합니다.

♦ 케이블에는 외부 표면의 85 % 이상을 덮는 스크린 (호일)이 있어야합니다. 케이블 끝에서 실드가 울리고 커넥터 핀에 연결되어야합니다.

이러한 요구 사항을 충족하는 케이블에는“IEEE Std 1284–1994 규격”이라는 레이블이 붙어 있습니다. 그들은 최대 10 미터의 길이를 가질 수 있으며 유형 지정은 표에 나와 있습니다. 1.10.

표 1.10. 케이블 유형 IEEE 1284

| 타입 | 복호화 | 커넥터 1 | 커넥터 2 |

| 아마 | A 형 남성-A 형 남성 | A (플러그) | A (플러그) |

| 아마 프 | A 형 남성-A 형 여성 | A (플러그) | (소켓) |

| Ab | 유형 A 수-투어 B 플러그-표준 프린터 케이블 | A (플러그) | 안으로 |

| AC | 유형 A 수컷-플러그가있는 투어-새 프린터 케이블 | A (플러그) | 와 |

| BC | 투어 인 플러그-플러그 타입 | 안으로 | 와 |

| CC | Ture C 플러그-C 형 플러그 | 와 | 와 |

1.3.8. IEEE 1284 표준 개발

다음은 핵심 IEEE 1284 표준에 대한 추가 사항입니다.

♦ IEEE P1284.1 "전송 독립적 인 프린터 / 스캐너 인터페이스 (TIP / SI)를위한 정보 기술 표준." 이 표준은 NPAP (Network Printing Alliance Protocol) 기반 스캐너 및 프린터의 관리 및 유지 보수를 위해 개발되고 있습니다.

♦ IEEE P1284.2 "IEEE 표준에 대한 테스트, 측정 및 적합성 표준. 1284”는 IEEE 1284와 호환되는 포트, 케이블 및 장치를 테스트하기위한 표준입니다.

♦ IEEE P1284.3 "IEEE 표준 인터페이스 및 프로토콜 확장 표준. 1284 호환 주변기기 및 호스트 어댑터 포트”-응용 프로그램 소프트웨어의 드라이버 및 장치 사용 표준. DOS 드라이버에서 EPP 사용을위한 BIOS 사양이 허용됩니다. 멀티플렉서를 통해 연결된 장치 그룹 또는 장치 그룹에서 단일 포트의 공유 사용을위한 표준이 개발되고 있습니다.

♦ IEEE P1284.4 "IEEE 표준 데이터 전송 및 논리 채널 표준. 1284 인터페이스 "병렬 포트를 통한 안정적인 데이터 전송을위한 패킷 프로토콜 구현을 목표로합니다. 기본은 Hewlett-Packard의 MLC (Multiple Logical Channels) 프로토콜이지만 표준의 최종 버전에서는 호환성이 보장되지 않습니다.

1.4. LPT 포트 시스템 지원

LPT 포트에 대한 시스템 지원에는 설치된 포트 검색 및 인쇄 서비스가 포함됩니다 (Int 17h, 8.3.3 절 참조). 초기 POST 테스트 동안 BIOS는 3BCh, 378h 및 278h에서 병렬 포트를 확인하고 감지 된 포트의 기본 주소를 BIOS Data Area 0 : 0408h, 040Ah, 040Ch, 040Eh 셀에 배치합니다. 이 셀은 포트 주소 LPT1-LPT4를 저장하며, 주소의 0 값은이 번호의 포트가 없음을 나타냅니다. 셀 0 : 0478, 0479, 047A, 047B에서 이러한 포트의 시간 초과를 지정하는 상수가 지정됩니다.

포트 검색은 일반적으로 매우 원시적으로 수행됩니다. 테스트 바이트 (AAh 또는 55h)가 기본 주소 (의도 한 포트의 데이터 레지스터)에 표시되고 동일한 주소의 입력이 수행됩니다. 읽은 바이트가 기록 된 바이트와 일치하면 LPT 포트가있는 것으로 가정합니다. 해당 주소는 BIOS 데이터 영역 셀에 있습니다. 기본 포트 주소는 프로그래밍 방식으로 변경 될 수 있습니다. 표준 검색 주소 목록에는 위의 3 개만 포함되므로 LPT4 포트 주소는 BIOS 자체에서 설정할 수 없습니다.

감지 된 포트는 초기화됩니다-제어 레지스터에 기록하여 신호 Init #가 생성 및 제거 된 후 인터페이스 신호의 초기 상태에 해당하는 값 0Ch가 기록됩니다. 경우에 따라 Init # 신호는 하드웨어 재설정 순간부터 OS 부팅시 포트가 초기화 될 때까지 활성화됩니다. 이것은 컴퓨터를 다시 시작하는 동안 프린터의 작동 상태에서 확인할 수 있습니다. 온라인 표시기가 오랫동안 꺼집니다. 이 현상의 결과로 OS를로드하기 전에 Print Screen 키를 눌러 화면을 인쇄 할 수 없습니다 (예 : BIOS 설정 매개 변수).

1.5. 병렬 포트 및 PnP

LPT 포트에 연결된 대부분의 최신 주변 장치는 1284 표준 및 PnP 기능을 지원합니다. 이러한 기능을 지원하기 위해 하드웨어 관점에서 볼 때 컴퓨터는 1284 표준을 준수하는 인터페이스 컨트롤러를 갖기에 충분합니다. 연결된 장치가 PnP를 지원하는 경우 모드 일치 프로토콜 1284를 사용하여 가능한 교환 모드에 대해 컴퓨터의 "관심 사항"을 나타내는 포트와 "협상"할 수 있습니다. 또한 PnP가 작동하려면 연결된 장치가 운영 체제에 필요한 모든 정보를 알려야합니다. 최소한 제조업체 식별자, 모델 및 지원되는 명령 집합입니다. 보다 상세한 장치 정보는 클래스 식별자, 상세한 설명 및 호환성이 보장되는 장치 식별자를 포함 할 수있다. 이 장치를 지원하기 위해 수신 된 정보에 따라 운영 체제는 필요한 소프트웨어를 설치하기위한 단계를 수행 할 수 있습니다.

PnP를 지원하는 장치는 부팅 단계에서 OS에서 인식합니다. 물론 인터페이스 케이블을 통해 포트에 연결되어 있고 전원이 켜져있는 경우입니다. Windows가이 포트의 레지스트리에 작성된 것과 다른 연결된 PnP 장치 (또는 새 장치)를 발견하면 OS 배포 키트 또는 새 장치와 함께 제공된 패키지에서 장치에 필요한 드라이버를 설치하려고합니다. Windows에서 새로 연결된 PnP 장치를 확인하지 않으려는 경우 포트 또는 케이블 고장 일 수 있습니다. 장치가 SelectIn # 연결이없는 저렴한 "양방향"케이블 (LPT 포트의 핀 17 및 Centronics 커넥터의 핀 36)에 연결되어 있으면 PnP 시스템이 작동하지 않습니다.

1.6. LPT 포트 사용

일반적으로 LPT 포트는 프린터를 연결하는 데 사용되지만 (8.3.1 절 참조),이 사용에는 적용되지 않습니다.

사용 된 포트의 모드에 따라 병렬 인터페이스를 통해 두 대의 컴퓨터를 연결하는 데 다양한 케이블이 사용됩니다. 가장 간단하고 느린 것은 모든 포트에서 작동하는 니블 모드입니다. 이 모드의 경우 케이블에 10 개의 신호와 하나의 공통 와이어가 있으면 충분합니다. 케이블 커넥터의 배선은 표에 나와 있습니다. 1.11. 이 케이블을 사용한 두 대의 PC 연결은 MS-DOS의 Interlnk 또는 Norton Commander와 같은 표준 소프트웨어에서 지원됩니다. 1.3.1 절에서 설명한 것과 다른 프로토콜이 사용된다는 점에 유의하십시오.

표 1.11. PC-PC 통신 케이블 (4 비트)

| X1, PC 커넥터 # 1 | X2, PC 커넥터 # 2 | ||

| 비트 | 연락 | 연락 | 비트 |

| DR.0 | 2 | 15 | SR.3 |

| DR.1 | 3 | 13 | SR.4 |

| DR.2 | 4 | 12 | Sr.5 |

| DR.3 | 5 | 10 | SR.6 |

| DR.4 | 6 | 11 | SR.7 |

| SR.6 | 10 | 5 | DR.3 |

| SR.7 | 11 | 6 | DR.4 |

| Sr.5 | 12 | 4 | DR.2 |

| SR.4 | 13 | 3 | DR.1 |

| SR.3 | 15 | 2 | DR.0 |

| GND | 18-25 | 18-25 | GND |

커넥터 X1 및 X2-DB25-P (플러그).

두 컴퓨터 간의 고속 통신도 ECP 모드에서 수행 할 수 있습니다 (EPP 모드는 두 컴퓨터의 버스 입력 / 출력주기 동기화가 필요하기 때문에 불편합니다).

테이블에서. 1.12 케이블 배선은 저자의 이전 책과 유사한 표에 표시되어 있으며 (참조 및) 오류가있었습니다 (접점 13과 15가 반전 됨). 케이블의 모든 신호 중에서 PeriphRequest # (핀 15) 만 사용되지 않습니다. 두 컴퓨터의 데이터 포트가 출력 모드에있을 때 너무 높은 전류가 흐르지 않도록 순차적 저항 (0.5–1kOhm)을 데이터 라인의 회로에 삽입하는 것이 좋습니다. 이 상황은 컴퓨터 통신 소프트웨어가 아직 실행되고 있지 않을 때 발생합니다. ECP 모드에서의 통신은 Windows 9x에서 지원되며, PARALINK.VxD 드라이버는 이러한 OS의 제공 패키지에 포함되어 있지만 내부 오류로 인해 작동하지 않습니다. 이 드라이버의 패치와 테스트 유틸리티 및 필요한 설명은 네트워크 (www.lpt.com, www.lvr.com/parport.htm)에서 찾을 수 있습니다.

표 1.12. ECP 모드 및 바이트 모드의 PC-PC 통신 케이블

| 커넥터 X1 | 커넥터 x2 | ||

| 연락 | ECP의 이름 | ECP의 이름 | 연락 |

| 1 | Hostclk | 페리 ip 크 | 10 |

| 14 | Hostack | 페리 핵 | 11 |

| 17 | 활성 | Xflag | 13 |

| 16 | ReverseRequest # | AskReverse # | 12 |

| 10 | 페리 ip 크 | Hostclk | 1 |

| 11 | 페리 핵 | Hostack | 14 |

| 12 | AckReverse # | ReverseRequest # | 16 |

| 13 | Xflag | 활성 | 17 |

| 2, 3…9 | 자료 | 자료 | 2, 3…9 |

메인 스트림이 입력되므로 포트가 양방향 모드 (Bi-Di)를 제공하는 경우에만 스캐너를 LPT 포트에 연결하는 것이 효과적입니다. 이 모드가 스캐너 (또는 가능하지 않은 EPP)에서 지원되는 경우 ECP 포트를 사용하는 것이 좋습니다.

외부 드라이브 (Iomega Zip 드라이브, CD-ROM 등), LAN 어댑터 및 기타 대칭 입 / 출력 장치의 연결에는 고유 한 특성이 있습니다. SPP 모드에서는 장치의 속도 저하와 함께이 모드의 기본 비대칭 성이 눈에 :니다. 데이터 읽기는 쓰기 속도의 2 배 (매우 느림)입니다. 양방향 모드 (Bi-Di 또는 PS / 2 Tour 1)를 사용하면 이러한 비대칭 성을 제거 할 수 있습니다. 속도는 동일합니다. EPP 또는 ESR로 전환해야만 정상 속도를 얻을 수 있습니다. EPP 또는 ECP 모드에서 LPT 포트 연결은 ISA 컨트롤러를 통한 연결 속도와 거의 같습니다. 표준 버스 인터페이스가있는 장치를 인터페이스 변환기 (예 : LPT-IDE, LPT-SCSI, LPT-PCMCIA)를 통해 LPT 포트에 연결하는 경우에도 마찬가지입니다. 어댑터를 통해 시스템의 LPT 포트에 연결된 IDE 하드 드라이브는 SCSI 장치로 표현 될 수 있습니다 (이는 소프트웨어 관점에서 더 논리적입니다).

테이블에서. 1.13은 다양한 모드에서 LPT 포트 커넥터의 단자의 목적과 표준 포트의 레지스터 비트에 대한 대응을 설명합니다.

표 1.13. SPP, ECP 및 EPP 모드에서 LPT 포트 커넥터 및 레지스터 비트의 핀 할당

| 연락 | I / O | 비트 ¹ | SPP | ECP | EPP |

| 1 | 오 / 난 | CR.0 | 스트로브 # | Hostclk | 쓰기 # |

| 2 | 오 / 난 | DR.0 | 데이터 0 | 데이터 0 | 데이터 0 |

| 3 | 오 / 난 | DR.1 | 데이터 1 | 데이터 1 | 데이터 1 |

| 4 | 오 / 난 | DR.2 | 데이터 2 | 데이터 2 | 데이터 2 |

| 5 | 오 / 난 | DR.3 | 데이터 3 | 데이터 3 | 데이터 3 |

| 6 | 오 / 난 | DR.4 | 데이터 4 | 데이터 4 | 데이터 4 |

| 7 | 오 / 난 | DR.5 | 데이터 5 | 데이터 5 | 데이터 5 |

| 8 | 오 / 난 | DR.6 | 데이터 6 | 데이터 6 | 데이터 6 |

| 9 | 오 / 난 | DR.7 | 데이터 7 | 데이터 7 | 데이터 7 |

| 10 | 나 | SR.6 | 승인 번호 | 페리 ip 크 | INTR # |

| 11 | 나 | SR.7 | 바쁜 | 페리 핵 | 기다림 # |

| 12 | 나 | Sr.5 | 페이퍼 엔드 | AckReverse # | -² |

| 13 | 나 | SR.4 | 선택 | Xflag | -² |

| 14 | 오 / 난 | CR.1 | 자동 LF # | Hostack | DataStb # |

| 15 | 나 | SR.3 | 오류 # | PeriphRequest # | -² |

| 16 | 오 / 난 | CR.2 | 초기화 # | ReverseRequest # | 재설정 # |

| 17 | 오 / 난 | CR.3 | #에서 선택 | 활성 | AddrStb # |

¹ "\\"기호는 반전 된 신호를 나타냅니다 (레지스터의 1은 로우 라인 레벨에 해당).

² 사용자 정의.

1.7. LPT 포트 구성

병렬 포트 제어는 포트 하드웨어의 사전 구성 (Setup)과 응용 프로그램 또는 시스템 소프트웨어에 의한 작동 모드의 현재 (작동) 전환의 두 단계로 구분됩니다. 온라인 전환은 구성 중에 허용되는 모드 제한 내에서만 가능합니다. 이를 통해 하드웨어를 소프트웨어와 일치시키고 잘못된 프로그램 동작으로 인한 잘못된 전환을 차단할 수 있습니다.

LPT 포트의 구성은 실행에 따라 다릅니다. ISA 또는 ISA + VLB 슬롯에 설치된 확장 카드 (멀티 카드)에있는 포트는 카드 자체의 점퍼로 구성됩니다. 시스템 보드의 포트는 BIOS 설정을 통해 구성됩니다.

구성 할 매개 변수는 다음과 같습니다.

♦ 기본 주소는 3BCh, 378h 또는 278h입니다. 초기화하는 동안 BIOS는이 순서대로 주소를 기준으로 포트의 가용성을 확인하고 논리 이름 LPT1, LPT2, LPT3을 탐지 된 포트에 할당합니다. 3BCh 주소는 MDA 또는 HGC 카드에 포트 어댑터가 있습니다. 대부분의 포트는 기본적으로 378h로 구성되며 278h로 전환 할 수 있습니다.

♦ 사용 된 인터럽트 요청 라인 : LPT-IRQ7, LPT2-IRQ5 용. 일반적으로 프린터의 인터럽트는 활성화되지 않으며이 부족한 리소스를 저장할 수 있습니다. 그러나 ECP (또는 Fast Centronics) 고속 모드를 사용하는 경우 인터럽트 작동으로 성능이 크게 향상되고 프로세서로드가 줄어 듭니다.

♦ ECP 및 Fast Centronics 모드에 DMA 채널 사용-해상도 및 DMA 채널 번호.

♦ 포트 작동 모드 :

SPP-포트는 표준 단방향 프로그램 제어 모드에서만 작동합니다.

PS / 2, 일명 양방향-채널을 반전시키는 기능 (설정 CR.5 \u003d 1)에 의해 SPP와 다릅니다.

Fast Centronics-FIFO 버퍼 및 가능하면 DMA를 사용하여 Centronics 프로토콜의 하드웨어 생성;

EPP-레지스터 사용에 따라 포트는 SPP 또는 EPP 모드에서 작동합니다.

ECP-기본적으로 SPP 또는 PS / 2 모드로 전환되며 ECR에 기록하면 모든 ECP 모드로 전송할 수 있지만 코드 100을 ECR에 기록하여 EPP 로의 전송은 보장되지 않습니다.

ECP + EPP는 ECP와 동일하지만 ECR 모드 코드 100을 작성하면 포트가 EPP로 전송됩니다.

EPP, ECP 또는 Fast Centronics 모드 만 선택해도 연결된 컨트롤러와의 교환 속도는 증가하지 않지만 드라이버와 컨트롤러는 "이해"범위 내에서 최적 모드를 설정할 수 있습니다. 대부분의 최신 드라이버와 응용 프로그램은 효과적인 모드를 사용하려고하므로 적절한 이유없이 간단한 모드를 설치하여 "날개를 자르는"것은 가치가 없습니다.

프린터 및 스캐너는 ECP 모드를 원할 수 있습니다. Windows (3.x, 9x 및 NT)에는이 모드에 대한 시스템 드라이버가 있습니다. DOS에서 ECP를 통한 인쇄는 다운로드 가능한 특수 드라이버에서만 지원됩니다.

병렬 포트에 연결된 네트워크 어댑터, 외부 드라이브 및 CD-ROM은 EPP 모드를 사용할 수 있습니다. 이 모드에서는 특수 드라이버가 아직 적용되지 않았습니다. EPP 지원은 장치 자체의 드라이버에 포함되어 있습니다.

1.8. 병렬 포트 장애 및 테스트

시스템에 존재하는지 확인하여 병렬 포트 테스트를 시작하는 것이 합리적입니다. 설치된 포트의 주소 목록은 OS를로드하기 전에 화면에 BIOS가 표시하는 표에 나타납니다. 테스트 프로그램을 사용하거나 디버거를 사용하여 BIOS 데이터 영역에서 직접 목록을 볼 수 있습니다.

BIOS가 물리적으로 설치된 것보다 적은 수의 포트를 감지하면 두 포트에 동일한 주소가 할당 될 가능성이 높습니다. 동시에 충돌하는 포트의 작동이 보장되지 않습니다. 동시에 신호를 출력하지만 상태 레지스터를 읽을 때 버스에서 충돌이 발생하면 데이터가 손상 될 수 있습니다. 진단 플러그 (루프 백)가없는 포트의 소프트웨어 테스트는 출력 레지스터의 데이터를 읽으므로 오류가 표시되지 않으며 모든 충돌 (개별적으로 작동하는 포트)과 일치합니다. 이것은 정확히 포트를 확인할 때 BIOS가 수행하는 테스트 종류입니다. 이 상황은 포트를 순차적으로 설치하고 목록에 나타나는 주소를 관찰하여 처리해야합니다.

물리적으로 하나의 포트만 설치되어 있고 BIOS가이를 감지하지 못하면 구성 중에 포트가 비활성화되었거나 실패한 것입니다 (대부분 연결 규칙 위반으로 인해). 운이 좋으면 슬롯의 보드를 "전환"하여 오작동이 제거됩니다. 때로는 접점에 문제가 있습니다.

이러한 "기적"도 관찰됩니다. Windows 95 이후 DOS가 따뜻하게 재부팅되면 포트가 보이지 않으며 응용 프로그램은 MS-DOS에서 인쇄 할 수 없습니다. 그러나 재부팅 후 DOS 포트가 제 위치에 있습니다. 이 현상은 싸움보다 참기 쉽습니다.

진단 프로그램을 사용하여 포트를 테스트하면 출력 레지스터와 특수 플러그를 사용할 때 입력 라인을 확인할 수 있습니다. 포트 (12)와 입력 (5)의 출력 라인 수가 다르기 때문에 수동 스터브를 사용하여 포트를 완전히 점검하는 것은 근본적으로 불가능합니다. 테스트 프로그램마다 다른 스텁을 사용해야합니다 (그림 1.8).

그림. 1.8. LPT 포트 테스트를위한 스텁 회로 : a-CheckIt, b-Norton Diagnostics

LPT 포트로 작업 할 때 발생하는 대부분의 문제는 커넥터와 케이블로 인해 발생합니다. 포트, 케이블 및 프린터를 확인하기 위해 널리 사용되는 진단 프로그램 (CheckIt, PCCheck 등)의 특수 테스트를 사용할 수 있습니다. 문자 파일을 프린터로 간단하게 인쇄 할 수 있습니다.

♦ DOS 관점에서 출력 된 파일이 통과하고 (이름이 LPTn 또는 PRN 인 장치로 파일을 복사하는 것이 빠르고 성공한 경우) 프린터 (서비스 가능)가 단일 문자를 인쇄하지 않은 경우-Strobe # 회로의 열린 (커넥터의 핀이 아님) 것입니다 .

♦ 프린터가 온라인 상태에 있고 준비되지 않았다는 메시지가 표시되면 통화 중 라인에서 원인을 찾으십시오.

♦ 정상 모드 (SPP)의 포트에 연결된 프린터가 정상적으로 인쇄되고 ECP 모드로 전환이 실패하면 케이블이 IEEE 1284의 요구 사항을 충족하는지 확인해야합니다 (위 참조). 스위칭되지 않은 전선이있는 저렴한 케이블은 일반적으로 50-100 Kb / s의 속도로 작동하지만 ECP에서 제공하는 1-2 MB / s의 속도에서는 특히 2m 이상의 길이에서 작동하지 않을 권리가 있습니다.

♦ PnP 프린터 드라이버를 설치할 때 "양방향 케이블"을 사용하라는 메시지가 표시되면 DB-25 커넥터의 17 번 트랙을 Centronics 커넥터의 36 번 트랙에 연결했는지 확인하십시오. 이 연결은 원래 예상되었지만 여러 케이블에서 누락되었습니다.

♦ 프린터가 인쇄 정보를 잘못 해석하면 데이터 라인이 끊어 질 수 있습니다. 이 경우 인쇄 된 모든 문자에 대해 일련의 코드가 포함 된 파일을 사용하는 것이 편리합니다. 파일이 일부 문자 또는 해당 그룹의 반복으로 인쇄되는 경우 반복 빈도로부터 인터페이스 데이터의 댕글 링 와이어를 쉽게 계산할 수 있습니다. 동일한 파일을 사용하여 프린터의 하드웨어 Russification을 편리하게 확인할 수 있습니다.

LPT 포트의 하드웨어 인터럽트가 항상 사용되는 것은 아닙니다. PRINT DOS 백그라운드 인쇄 프로그램조차도 포트와 함께 작동하여 상태를 폴링하고 서비스 프로세스는 타이머 중단으로 시작됩니다. 따라서 포트의 인터럽트 회로와 관련된 오작동은 종종 나타나지 않습니다. 그러나 진정한 멀티 태스킹 운영 체제 (예 : NetWare)는 인터럽트를 통해 포트와 작동하려고합니다. 원격 제어 포트 또는 더미에 연결해야만 인터럽트 라인을 테스트 할 수 있습니다. LAN 어댑터를 인터럽트 채널에 결함이있는 포트에 연결하면 작동하지만 속도가 매우 느릴 수 있습니다. 모든 요청에 \u200b\u200b대해 응답이 수십 초 지연됩니다-어댑터에서 수신 한 패킷이 인터럽트에 의해 수신되지 않습니다 (즉시 도착)이지만 외부 시간 초과에 따라

병렬이라고도하는 Lpt 포트는 가장 오래된 PC 포트 중 하나입니다. 오늘날 이러한 포트를 모든 마더 보드에서 사용할 수는 없지만 여전히 일부 배포판이 있으므로 컴퓨터와 사무 기기, 특히 프린터를 사용하는 많은 사용자에게 그것이 무엇인지 알아내는 것이 매우 흥미 롭습니다.

먼저 약어 lpt 포트 자체의 의미를 이해해야합니다. 따라서 LPT는 여러 영어 단어의 조합, 즉 라인 인쇄 터미널의 감소를 의미합니다. 러시아어로 번역 된 LPT는 라인 프린터 터미널을 의미합니다. 이름을 기반으로하여 주로 프린터를위한 것임을 알 수 있습니다. 그러나 이론적 인 관점에서 일부 다른 장치도 LPT에 연결할 수 있습니다. 이를 위해 특수 어댑터-어댑터 lpt를 사용하십시오. 사용자 포트에 다른 이름 (프린터 포트)이 추가되어 있어야합니다.

일반적으로 lpt 포트는 다소 오랜 개발 역사를 가지고 있습니다. 그것은 Centronics의 직원에 의해 개발되었으며, 지난 세기의 70 년대 초에 도트 매트릭스 인쇄 장치 생산을 전문으로했습니다. 80 년대 초이 프린터 포트는 IBM에서 널리 사용되어 PC에서 사용되었습니다. 그 10 년 동안 lpt-port는 그 당시 고속으로 장치를 연결하는 데 필요한 표준 옵션이되었습니다.

처음에 LPT 인터페이스는 여러 버전으로 도입되었습니다. 또한 원본 버전에서는 단방향이었습니다. 그것의 도움으로 정보를 주변 장치에만 독점적으로 전송할 수있었습니다. 물론 이런 종류의 상황은 많은 사용자에게 적합하지 않았습니다. 그 당시 이미 양방향 데이터 전송이 필요한 인쇄 장치가 발행되었습니다. 그렇기 때문에 개발자들은 얼마 후 LPT1 인터페이스를 여러 번 개선해야했습니다. 이 프로세스는 IEEE 1284라는 표준이 도입 될 때까지 지속되었으므로 개발자는 최종 포트 체계를 제시했습니다. 새로운 표준은 여러 가지 다른 작동 모드를 지원했습니다. 또한 이전 표준과 호환되었습니다. 최종 버전에서 프린터 인터페이스는 그 당시 상당히 빠른 속도의 정보 전송을 지원할 수 있었으며 5Mb / s에 도달했습니다!

병렬 포트는 어떻게 작동합니까?

병렬 LPT라는 이름은 연결된 케이블의 데이터 전송이 병렬로 수행되므로 여러 도체가 동시에 사용되기 때문입니다. 이 때문에 메기와는 크게 다르기 때문에 일관성이 있습니다. LPT에 연결하는 케이블의 도체 수는 일반적으로 8입니다. 또한 제어 신호를 전송하도록 설계된 여러 라인에 위치 할 수 있습니다. 따라서, LPT와 비교하여 포트의 사용은 많은 강한 한계와 단점이있다.

Centronics 포트가 프린터와 PC 사이의 연결을 설정하는 데 더 많이 사용되었다는 사실에도 불구하고, 다른 용도로 사용되었습니다. 예를 들어 LPT를 사용하면 두 대의 개인용 컴퓨터를 서로 직접 연결할 수 있습니다.이를 위해 일반적으로 인터링크 케이블이 사용됩니다. 이더넷 네트워크 카드가 널리 보급 될 때까지이 유형의 연결은 매우 인기가있었습니다. 물론, 사용자에게 매우 빠른 정보 전송 속도를 제공 할 수는 없었지만, 그럼에도 불구하고 그 기간 동안 두 대의 컴퓨터를 서로 연결하는이 방법은 거의 유일한 방법이었습니다. 병렬 포트에 연결하기 위해 특별히 설계된 전자 유형의 특수 키도 추가해야합니다.

LPT의 기능에 대하여

위에서 언급했듯이 LPT는 com과 달리 병렬 데이터 전송을 지원합니다. 개인용 컴퓨터의 첫 번째 모델에서 그는 가장 빠른 컴퓨터 중 하나였습니다. 인터페이스는 여러 회선을 통해 정보를 전송하는 기능으로 인해 아키텍처에서 PC에 사용되는 버스와 거의 유사합니다. 그러나 정확하게 5 미터를 초과 할 수없는 케이블의 길이를 제한하는 것은 이런 종류의 상황입니다. 그렇지 않으면 PC와 프린터 사이의 연결에 간섭이 지속적으로 발생합니다.

일반적인 데이터 전송을 구성하려면 일반적으로 10 개의 신호선이 필요합니다. 나머지 라인은 Centronics 케이블 표준과의 호환성을 위해 사용됩니다. LTP 신호 라인에 사용되는 최대 전압 파라미터는 일반적으로 + 5V입니다.

포트 커넥터 및 Centronics 케이블

우리가 병렬 포트 커넥터에 관해 이야기한다면, 지난 세기의 90 년대 중반 까지이 요소는 일반적으로 소위에 있었지만 마더 보드 자체에 위치합니다. 확장 슬롯에 삽입 된 멀티 카드. LPT 출력은 25 핀 DB25 커넥터입니다.

개인 포트를 사용하여 개인용 컴퓨터와 인쇄 사무 기기를 연결하려면 Centronics 케이블을 사용해야합니다. 동시에 사무 기기에서 사용 가능한 커넥터는 36 핀입니다. 따라서이 케이블의 주요 특징은 양쪽에 서로 다른 두 개의 커넥터가 있다는 것입니다.

또한 Centronics 커넥터는 개인용 컴퓨터의 마더 보드 용으로 설계된 케이블 커넥터라고 불리는 경우가 많지만 실제로는 프린터 커넥터입니다. 하나는 36 개의 연락처를 포함합니다. LPT 전용으로 설계된 커넥터는 Amphenolstacker라고합니다. 적절한 이름으로 모든 것을 호출하려면 이름의 이러한 차이점을 알아야합니다.

요약

결론적으로, 병렬 라인 인쇄 터미널 포트는 PC 인터페이스이며 지금까지는 상당히 오래되었다고 말할 수 있습니다. 지난 세기의 지난 수십 년 동안 광범위한 배포에도 불구하고 오늘날이 포트는 컴퓨터 장비, 사무 장비 및 소프트웨어를 생산하는 많은 회사의 많은 지원을받지 않습니다. 그럼에도 불구하고 LPT는 여전히 오래된 PC 모델과 인쇄 장치에서 성공적으로 사용됩니다. 그러나 컴퓨터와 기존 프린터를 연결하려면 com-lpt 어댑터가 필요합니다. 오늘날 원칙적으로 판매시 찾을 수 있지만 필요한 지식과 기술이 있으면 그러한 어댑터를 완전히 숨길 수 있습니다.

이 사이트가 존재하는 동안 나는 종종 다음과 같은 질문을 할 수 있습니다.

결국, 나는이 문제를 더 자세하게 설명하고 기사를 작성하기로 결정했습니다. 예, 실제로 LPT 포트가있는 고정 PC를 찾아야합니다 (즉, 모든 "어머니"와 멀리 떨어져 LPT 포트가 번들로 제공됨). 랩톱에 대해서는 일반적으로 말할 필요가 없습니다. 최신 LPT 포트 모델은 전혀 사용되지 않습니다. DELL과 같은 매우 비싸고 전문화 된 기계 만이이 포트를 보유 할 수 있습니다.

또한 현재 판매 중에 LPT-USB 어댑터라는 장치를 자유롭게 구입할 수 있습니다.

이 장치는 다양한 프린터, 스캐너 등과 완벽하게 호환됩니다. 우리는 어댑터를 USB 포트에 연결하고 드라이버를 설치합니다. 장치 관리자를 봅니다. 아마도 지점에서 "LPT / COM 포트" 둘 중 어느 것도 나타나지 않았다 (예외는 있지만). 예를 들어, 이름이 이상한 장치가있는 새 분기 중 하나 일 수 있습니다. LPT1USB 또는 이상한 항목 "LPT 프린터를 지원하는 USB 장치". 우리는 위의 기사에서 몇 가지 예를 실행하려고합니다. 그리고 그것은 여기에 없었습니다. 아무것도 작동하지 않습니다. 우리는 포트 주소 LPT1을 시도합니다-아무것도 작동하지 않습니다. 우리는 LPT2 포트의 주소를 시도합니다. 불행히도 쿼리에서 주소의 현대화도 아무런 영향을 미치지 않습니다 .LED가 켜지지 않고 켜지지 않았습니다.

여기서 중요한 사항을 이해하려면 마더 보드에서 튀어 나오는 일반적인 "천연 철"LPT 포트 (LPT1)로 돌아갑니다. 장치 관리자로 가서 포트 속성을 살펴 보겠습니다. 거기서 우리는 그런 그림을 볼 것입니다. 시스템이 기본 I / O 주소 0x378과 인터럽트 요청 번호 7을 등록했음을 분명히 알 수 있습니다. 모든 것이 정확합니다.

이제 프로그래밍 수준으로 뛰어 들어보십시오. 위 기사의 예에서 우리는 주소 0x378이 할당 된 실제 기존 I / O 레지스터와 직접 통신하는 합법적이고 불법적 인 방법으로 I / O 보호 시스템을 우회합니다. 여기에 모든 것이 명확합니다. Windows가 함수 API 호출을 사용하여 LPT 포트를 사용하는 것이 좋습니다. OpenFile (), WriteFile (), ReadFile (). LPT 포트를 사용하여 외부 장치 (예 : 프린터)와 병렬 인터페이스의 정보를 교환하는 응용 프로그램도 그렇게합니다. 그는 레지스터의 비트에 설치할 작업이 없습니다 자료 종교적 단위. 그는 (응용 프로그램) 데이터 패킷을 보내면되고, "풀"하고 읽을 행이있는 사람은 그다지 관심이 없습니다. 이러한 작업은 LPT 포트 시스템 드라이버에서 수행합니다. OS를로드 할 때 메모리에로드됩니다. 함수를 호출 할 때 OpenFile ( "LPT1", ....) 기본적으로 LPT1이라는 기호 이름을 가진 포트 드라이버를 사용합니다. 드라이버는 많은 모든 작업을 수행합니다-다른 프로세스에 대한 포트 액세스를 금지하고 데이터 전송 프로토콜의 매개 변수를 구성하며 실제로이 전송을 구현하지만 궁극적으로 OS의 커널 수준에서 LPT 포트의 개별 비트를 직접 제어합니다.

이제 USB-LPT 어댑터로 작업 해 봅시다. API 호출로 이상하게 보이지 않기 때문에 시작합시다. 우리는 발사 OpenFile ( "LPT1USB", ...) (이 어댑터가 장치 관리자에게 어떻게 호출되는지에 따라) 이것으로 어떻게됩니까? 사실 이제는 OS 포트의 LPT 드라이버가 아니라이 어댑터의 드라이버와 함께 작동합니다! 그게 속임수입니다! 사용자 응용 프로그램에서 데이터 패킷을 수신하고 USB 시스템 드라이버를 통해 필요한 형식으로이 패킷을 USB 컨트롤러로 전송합니다.이 "레그"는 와이어의 외부 LPT 소켓에서 튀어 나옵니다 (자세한 설명입니다). 주소 0x378 (0x278)의 레지스터에 액세스하는 힌트는 없습니다. 그들은 단순히 거기에 없습니다!

따라서이 섹션의 예제를 실행하고 주소 0x378 (이 "의사 포트"를 LPT1USB 또는 이와 유사한 이름으로 지정한 경우), 0x278 (LPT2 _...) 등을 직접 연결하려고하면 아무 일도 일어나지 않습니다. 그들은 단순히 거기에 없습니다! 그러나 API 호출을 통해 작동하는 프로그램은 아무것도 알지 못합니다. 모든 저수준 작업은 드라이버가 수행하며 응용 프로그램과 데이터 패킷이 어디로 갈 것인지 (실제 I / O 포트 또는 USB 호스트 컨트롤러로) 응용 프로그램에는 중요하지 않습니다! 장치 관리자에서 의사 포트 속성을 열어보십시오. 리소스 탭이 없습니까? 예, 그러나 일부 부적절한 값이 있거나 탭이 비활성화되어 있습니까? 그게 요점입니다.

왜 99 %입니까? Windows에서 본격적인 LPT1 포트로 정의한 자체 제작 USB-LPT 어댑터가 있기 때문에 완전히 일반 주소 0x378이 할당됩니다. 포트 핀에 대한 직접 호출이 성공했습니다! 그러나 이것은 매우 비표준 설계입니다 (주로 LPT1 포트의 기본 주소에 대한 호출을 가로채는 드라이버). 이 모든 것이 매우 신뢰할 수는 없으며 (OS 업데이트-디자인이 작동 능력을 잃습니다) 사용하기 위해서는 한 번만 사용하는 것이 좋습니다.

이상하게 보일 수도 있습니다. 항상 데스크탑 컴퓨터 또는 랩톱에 실제 LPT 포트를 추가 할 수 있습니다. 먼저, USB 어댑터를 즉시 잊어라. 이 문제를 해결하려면 구입해야합니다 PCI-LPT 데스크탑 PC 용 어댑터 (무료 PCI 슬롯이 필요함) 또는 PCMCIA-LPT 노트북 어댑터 (아래 사진 참조).

|

|

|

이러한 장치를 사용하는 경우 아무런 문제가 없습니다. 이들은 실제 "기본"LPT 포트로 정의됩니다. 해당 항목이 장치 관리자에 추가됩니다. "LPT / COM 포트". 포트 핀에 직접 액세스 할 수 있습니다.

병렬 포트 및 RPR

LPT-nop에 연결된 대부분의 최신 주변 장치는 1284 표준 및 Rpr 기능을 지원합니다. 이러한 기능을 지원하기 위해 하드웨어 관점에서 볼 때 컴퓨터는 1284 표준을 준수하는 인터페이스 컨트롤러를 갖기에 충분합니다. 연결된 장치가 RPR을 지원하는 경우 프로토콜 일치 모드 1284를 사용하여 가능한 교환 모드에 대해 컴퓨터의 "관심 사항"을 나타내는 포트와 "협상"할 수 있습니다. 또한 RPR이 작동하려면 연결된 장치가 운영 체제에 필요한 모든 정보를 알려야합니다. 최소한 제조업체 식별자, 모델 및 지원되는 명령 집합입니다. 보다 상세한 장치 정보는 클래스 식별자, 상세한 설명 및 호환성이 보장되는 장치 식별자를 포함 할 수있다. 이 장치를 지원하기 위해 수신 된 정보에 따라 운영 체제는 필요한 소프트웨어를 설치하기위한 단계를 수행 할 수 있습니다.

RPR을 지원하는 장치는 물론 인터페이스 케이블을 통해 포트에 연결되어 있고 전원이 켜져 있지 않는 한 로딩 단계에서 OS에 의해 인식됩니다. Windows가 지정된 포트 (또는 새 장치)의 레지스트리에 기록 된 것과 다른 연결된 Rpr 장치를 발견하면 OS 배포 키트 또는 새 장치와 함께 제공된 패키지에서 장치에 필요한 드라이버를 설치하려고합니다. Windows에서 새로 연결된 PPR 장치를 확인하지 않으려는 경우 포트 또는 케이블 고장 일 수 있습니다. RPR 시스템은 Selectln # 연결이없는 저렴한 "양방향"케이블 (LPT 포트의 핀 17 및 Centronics 커넥터의 핀 36)로 장치를 연결 한 경우 작동하지 않습니다.

일반적으로 LPT 포트는 프린터를 연결하는 데 사용되지만 (8.3.1 절 참조),이 사용에는 적용되지 않습니다.

두 대의 컴퓨터를 연결하려면사용되는 포트의 모드에 따라 다양한 인터페이스가 병렬 인터페이스에 사용됩니다. 가장 쉽고 느린 니블 모드 모두포트. 이 모드의 경우 케이블에 10 개의 신호와 하나의 공통 와이어가 있으면 충분합니다. 케이블 커넥터의 배선은 표에 나와 있습니다. 1.11. 이 케이블을 사용한 두 대의 PC 연결은 MS-DOS의 Interlnk 또는 Norton Commander와 같은 표준 소프트웨어에서 지원됩니다.

두 컴퓨터 간의 고속 통신도 ECP 모드에서 수행 할 수 있습니다 (EPP 모드는 두 컴퓨터의 I / O 버스주기 동기화가 필요하기 때문에 불편합니다).

연결 스캐너lPT 포트는 포트가 양방향 모드를 제공하는 경우에만 유효합니다 (비디),메인 스레드가 입력되었으므로. 이 모드가 스캐너 (또는 가능하지 않은 EPP)에서 지원되는 경우 ECP 포트를 사용하는 것이 좋습니다.

연결 외장 드라이브(Iomega Zip 드라이브, CD-ROM 등), lAN 어댑터다른 대칭 입출력 장치에는 고유 한 특성이 있습니다. SPP 모드에서 장치의 속도 저하와 함께이 모드의 기본 비대칭이 눈에 :니다. 데이터 읽기계속 두 배보다 느리다(매우 느림) 기록.신청 양방향정권 (바이 디또는 PS / 2 투어 1)이 비대칭을 제거하십시오- 속도는 같습니다.EPP 또는 ECP로 전환해야만 얻을 수 있습니다 정상작업 속도. EPP 또는 ECP 모드에서 LPT 포트 연결은 ISA 컨트롤러를 통한 연결 속도와 거의 같습니다. 인터페이스 변환기 (예 : LPT-IDE, LPT-SCSI, LPT-PCMCIA)를 통해 표준 버스 인터페이스가있는 장치를 LPT 포트에 연결할 때도 마찬가지입니다. 어댑터를 통해 시스템의 LPT 포트에 연결된 IDE 하드 드라이브는 SCSI 장치로 표현 될 수 있습니다 (소프트웨어 관점에서 더 논리적입니다).

2. 시리얼 인터페이스

데이터 전송을위한 직렬 인터페이스는 정보 비트가 순차적으로 전송되는 단일 신호 라인을 사용합니다. 따라서 인터페이스와 포트의 이름입니다. 영어 용어- 시리얼 인터페이스 그리고 시리얼 부분 (때로는 "직렬"로 잘못 번역 된 경우도 있음). 직렬 전송은 신호 라인 수를 줄이고 통신 범위를 증가시킵니다. 특징적인 특징은 비 TTL 신호의 사용입니다. 많은 직렬 인터페이스는 장치의 회로 접지에서 외부 (보통 입력) 신호의 전기 절연을 사용하므로 다양한 전위에서 장치를 연결할 수 있습니다. 아래에서는 인터페이스 RS-232C, RS-422A, RS-423A, RS-485, 전류 루프, MIDI 및 COM 포트를 고려합니다.

2.1. 시리얼 전송 방법

직렬 데이터 전송은 비동기 또는 동기 모드에서 수행 될 수 있습니다. 에서 비동기 각 바이트 앞에 시작 비트 패키지 시작의 수신자에게 신호를 보낸 후 데이터 비트 그리고 아마도 파 비트 (패리티). 패키지 완료 스톱 비트 소포 사이의 일시 정지를 보장합니다 (그림 2.1). 다음 바이트의 시작 비트는 정지 비트 이후 언제든지 전송됩니다. 즉, 전송간에 임의의 지속 시간이 일시 중지 될 수 있습니다. 항상 엄격하게 정의 된 값 (논리적 0)을 갖는 시작 비트는 송신기의 신호에 따라 수신기를 동기화하는 간단한 메커니즘을 제공합니다. 수신기와 송신기는 동일한 환율로 동작하는 것으로 이해된다. 수신기의 내부 클록 생성기는 기준 주파수 분배기 카운터를 사용하며 시작 비트가 수신 될 때 0으로 재설정됩니다. 이 카운터는 수신기가 후속 수신을 캡처하는 내부 게이트를 생성합니다.

비트. 게이트는 비트 간격의 중간에 위치하는 것이 이상적이며, 수신기와 송신기 속도가 약간 일치하지 않아도 데이터를 수신 할 수 있습니다. 8 개의 데이터 비트, 하나의 제어 및 하나의 정지 비트를 전송할 때, 데이터가 올바르게 인식 될 수있는 최대 허용 속도 불일치가 5 %를 초과 할 수 없음이 명백합니다. 내부 왜곡 카운터의 위상 왜곡 및 개별 작동을 고려하면 실제로 더 낮은 주파수 편차가 허용됩니다. 내부 발진기의 기준 주파수의 분할 비율이 낮을수록 (전송 주파수가 높을수록), 게이트를 비트 간격의 중간에 바인딩하는 데 오류가 커지고 주파수 매칭 요구 사항이 더 엄격 해집니다. 전송 주파수가 높을수록 수신 신호의 위상에 대한 에지 왜곡의 영향이 커집니다. 이러한 요소들의 상호 작용은 교환 주파수의 증가와 함께 수신기 및 송신기의 주파수의 일관성에 대한 요구 사항을 증가시킨다.

비동기 전송 형식을 사용하면 가능한 것을 식별 할 수 있습니다 전송 오류 :

» 송신 시작을 알리는 차이가 수신되고 논리 장치 레벨이 시작 비트 스트로브에 고정되면 시작 비트가 거짓으로 간주되고 수신기가 대기 상태로 다시 전환됩니다. 수신자가이 오류를보고하지 않을 수 있습니다.

“정지 비트에 할당 된 시간 동안 로직 0 레벨이 감지되면 정지 비트 오류가 기록됩니다.

"« 패리티가 적용되면 전송 후 데이터 비트가 전송됩니다. 제어 비트. 이 비트는 수락 된 계약에 따라 단일 데이터 비트 수를 짝수 또는 홀수로 보완합니다. 제어 비트 값이 유효하지 않은 바이트를 수신하면 오류가 해결됩니다.

형식 제어를 사용하면 줄 바꿈을 감지 할 수 있습니다.

이 경우, 논리 0이 허용되며, 이는 시작 비트로 처리되고 데이터 비트는 0으로 처리 된 다음 정지 비트 제어가 트리거됩니다.

비동기 모드에 대해 시리즈가 허용됩니다. 표준 환율 : 50, 75, 110, 150,300,600,1200,2400,4800,9600, 19200, 38400, 57600 및 115200 비트 / 초 때로는 "bps"측정 단위 대신 "baud"가 사용되지만 이진 전송 신호를 고려할 때 이는 올바르지 않습니다. 보드에서는 회선 상태 변경의 빈도를 측정하는 것이 일반적이며 통신 채널에서 비 이진 코딩 방법 (현대 모뎀에서 널리 사용됨)을 사용하면 비트 전송률 (bps)과 신호 변경 (baud)이 여러 번 다를 수 있습니다 (자세한 내용은 부록 A 참조) )

수량 데이터 비트 5, 6, 7 또는 8 일 수 있습니다 (5 및 6 비트 형식은 널리 배포되지 않음). 수량 스톱 비트 1, 1, 5 또는 2 일 수 있습니다 ( "1 및 반 비트"는 정지 간격의 길이 만 의미 함).

비동기 교환 PC를 사용하여 구현 COM 포트 프로토콜 사용 RS-232C.

동기식 전송 모드는 통신 채널의 일정한 활동을 가정합니다. 전송은 동기 바이트로 시작하여 바로 정보 비트 스트림이 뒤 따릅니다. 송신기에 전송할 데이터가없는 경우 지속적으로 동기화 바이트를 전송하여 일시 중지를 채 웁니다. 많은 양의 데이터를 전송할 때이 모드에서의 동기화 오버 헤드는 비동기보다 낮습니다. 그러나 동기 모드에서는 주파수 편차가 작더라도 수신 된 데이터가 왜곡 될 수 있으므로 수신기와 송신기의 외부 동기화가 필요합니다. 외부 동기화는 동기화 신호를 전송하기 위해 별도의 라인을 사용하거나 자체 동기화 데이터 인코딩을 사용하여 수신 신호로부터 수신 신호로부터 동기화 펄스를 추출 할 수있다. 어쨌든 동기 모드에는 고가의 통신 회선이나 터미널 장비가 필요합니다. PC의 경우 동기 교환 모드를 지원하는 특수 보드-SDLC 어댑터 (고가)가 있습니다. 주로 대형 IBM 시스템 (메인 프레임)과의 통신에 사용되며 널리 사용되지는 않습니다. 동기식 어댑터 중에서 V.35 인터페이스 어댑터가 현재 사용됩니다.

에 물리적 수준 직렬 인터페이스에는 전기 신호 전송 방식이 다른 다양한 구현이 있습니다. 여러 가지 관련 국제 표준이 있습니다. RS-232C, RS-423A, RS-422A 그리고 RS-485. 그림. 그림 2.2는 수신기와 송신기의 연결 다이어그램을 보여 주며 라인 길이 (L)와 최대 데이터 속도 (V)에 대한 제한 사항도 보여줍니다.

불평형 인터페이스 라인 RS-232C 그리고 RS-423A수신기 차동 입력이지만 공통 모드 내성이 가장 낮음 RS-423A 상황을 다소 완화시킵니다. 가장 좋은 매개 변수는 지점 간 인터페이스입니다. RS-422A 트렁크 (버스) 아날로그 RS-485, 대칭 통신 회선에 대한 작업. 각 신호를 전송하기 위해 별도의 (트위스트 된) 전선 쌍을 갖는 차동 신호를 사용합니다.

나열된 표준에서 신호가 나타납니다 잠재력. 공통 트랜스미터-수신기 회로를 통해 흐르는 전류 (“전류 루프”및 MIDI)에 유용한 직렬 인터페이스가 있습니다. 근거리 통신을 위해 무선 적외선 표준이 채택되었습니다. PC에서 가장 널리 보급 된 것은 목록에있는 표준 중 가장 단순했습니다. RS-232CcOM 포트로 구현됩니다. 산업 자동화에서 널리 사용됩니다 RS-485, 뿐만 아니라 RS-422A, 일부 프린터에서 발견되었습니다. 이러한 관련 인터페이스를 일치시키기위한 신호 변환기가 있습니다.

2.2. RS-232C 인터페이스

인터페이스는 데이터를 송수신하는 장비를 연결하도록 설계되었습니다 (OOD- 데이터 단말 장비 또는 ADF- 데이터 전송 장비; DTE-데이터 터미널 장비) 데이터 채널 터미널 장비 (AKD; DCE-데이터 통신 장비). ADF는 컴퓨터, 프린터, 플로터 및 기타 주변 장치 일 수 있습니다. AKD의 역할은 일반적으로 모뎀입니다. 연결의 궁극적 목표는 두 개의 ADF 장치를 연결하는 것입니다. 완전한 연결 다이어그램이 그림에 나와 있습니다. 2.3. 이 인터페이스를 사용하면 널 모뎀 케이블을 사용하여 장치를 직접 연결하여 한 쌍의 ADF 장치와 함께 원격 통신 채널을 제외 할 수 있습니다 (그림 2.4).

표준은 인터페이스 제어 신호, 데이터 전송, 전기 인터페이스 및 커넥터 유형을 설명합니다. 표준은 비동기 및 동기 교환 모드를 제공하지만 COM 포트만 지원 비동기 모드. 기능적으로 RS-232C CCITT V.24 / V.28 및 C2와 동일하지만 신호 이름이 다릅니다.

2.2.1. 전기 인터페이스

표준 RS-232C 비대칭 송신기 및 수신기 사용-신호는 공통 와이어-회로 접지를 기준으로 전송됩니다 (대칭 차동 신호는 다른 인터페이스에 사용됩니다-예를 들어, RS-422). 인터페이스 전기 연결을 제공하지 않습니다 장치. 논리 장치의 전압이 켜져 있음 수신기 입력 제어 신호 라인의 경우,이 상태를 ON 직렬 데이터 라인의 경우 (“On”)- 마크. +3 ... + 12 V의 논리적 범위는 논리적 0에 해당합니다. 제어 신호 라인의 경우 상태를 호출합니다 꺼짐 ( "끄기") 및 직렬 데이터 라인의 경우- 스페이스 -3 ... + 3 V의 범위는 데드 밴드이며 수신기의 히스테리시스를 결정합니다. 라인 상태는 임계 값을 초과 한 후에 만 \u200b\u200b변경되는 것으로 간주됩니다 (그림 2.5). 송신기의 출력에서 \u200b\u200b신호 레벨은 각각 -12 ...- 5 V 및 +5 ... + 12 V 범위에 있어야 유니티와 제로를 나타냅니다. 연결된 장치의 회로 접지 (SG) 간 전위차는 2V 미만이어야하며 전위차가 클수록 잘못된 신호 인식이 가능합니다. 인터페이스는 가용성을 가정 보호 접지 연결된 장치의 경우 두 장치 모두 AC 전원으로 공급되고 라인 필터가있는 경우

인터페이스 케이블 연결 및 분리 자체 전원 공급 장치를 생산해야합니다 전원이 꺼 졌을 때. 그렇지 않으면 스위칭시 장치의 불균형 전위차가 출력 또는 입력 (더 위험한) 인터페이스 회로에 적용되어 마이크로 회로를 비활성화 할 수 있습니다.

인터페이스 RS-232C 특별히 설계된 버퍼 수신기 미세 회로 (히스테리시스 및 바이폴라 신호 송신기 포함). 접지 및 스위칭 규칙을 따르지 않으면 일반적으로 불꽃 효과의 첫 번째 피해자입니다. 때로는 "침대"에 설치되어 교체가 용이합니다. 신호 컨디셔닝 칩 핀아웃 RS-232C 그림. 2.6. 종종 버퍼 회로는 인터페이스 LSI에 직접 포함됩니다. 이를 통해 제품 비용을 줄이고 보드 공간을 절약 할 수 있지만 사고 발생시 큰 재정 손실로 이어집니다. 신호 회로를 단락시켜 인터페이스 미세 회로를 비활성화 할 가능성은 거의 없습니다. 송신기의 단락 전류는 일반적으로 20mA를 초과하지 않습니다.

표준 RS-232C 지배하다 사용 된 커넥터 유형.

장비 ADF (COM 포트 포함) 설치하는 것이 일반적입니다 포크 (남성- "아빠") DB-25P 또는 더 컴팩트 한 옵션- DB-9P. 9 핀 커넥터에는 동기 작동에 필요한 추가 신호에 대한 접점이 없습니다 (대부분의 25 핀 커넥터에서는 이러한 접점이 사용되지 않습니다).

장비 AKD (모뎀) 설치 소켓(여성-“어머니”) DB-25Swm DB-9S.

이 규칙은 커넥터가 AKD 커넥터에 연결할 수 있습니다 ADF 직접 또는 접점이 "일대일"로 연결된 소켓 및 플러그가있는 전환 "직접"케이블을 통해. 어댑터 케이블은 9 ~ 25 핀 커넥터가있는 어댑터 일 수도 있습니다 (그림 2.7).

장비가 ADF 모뎀없이 연결되면 장치 커넥터 (플러그)가 서로 연결됩니다 널 모뎀 케이블 (제로 모뎀 또는 Z 모뎀), 양쪽 끝에 소켓이 있으며 그 접점은 그림 1에 표시된 회로 중 하나에 따라 십자로 연결됩니다. 2.8.

어떤 기기에서든 ADF 전원 콘센트가 설치되어 있습니다. 이는 모뎀 연결 케이블과 마찬가지로 직접 케이블을 사용하여 다른 장치에 연결해야한다는 절대적인 신호입니다. 콘센트는 일반적으로 모뎀을 통한 원격 연결이 제공되지 않는 장치에 설치됩니다.

테이블에서. 2.1은 COM 포트 및 기타 장비의 커넥터 접점의 목적을 보여줍니다. ADF). DB-25S 커넥터 핀은 EIA / TIA-232-E 표준으로 정의되며 DB-9S 커넥터는 EIA / TIA-574 표준으로 설명됩니다. 모뎀의 경우 회로와 접점의 이름은 동일하지만 신호의 역할 (입력 출력)이 반대로됩니다.

신호의 서브 세트 RS-232C 비동기 모드와 관련하여 PC의 COM 포트 관점에서 고려합니다. 신호의 활성 상태 ( "on")와 논리 단위 전송 된 데이터는 부정적인 잠재력 (-3V 이하) 인터페이스 신호의 상태가 "off"이고 논리적 제로-양수 (+ 3V 이상). 인터페이스 신호의 목적은 표에 나와 있습니다. 2.2.

1 *-8 비트 멀티 카드 루프.

2 *-마더 보드의 16 비트 멀티 카드 및 포트 루프. 3 *-마더 보드의 포트 루프 변형. 4 *-25 핀 커넥터의 넓은 루프.

2.2.2. 데이터 흐름 제어

데이터 흐름 (Flow Control)을 제어하기 위해 하드웨어와 소프트웨어의 두 가지 프로토콜 옵션을 사용할 수 있습니다. 때때로 흐름 제어가 승인과 혼동되기도하지만, 이는 하나의 목표를 달성하기위한 서로 다른 방법으로 송수신 속도를 조정합니다. 인정(핸드 쉐이킹)은 상품 수령에 대한 알림을 보내는 것을 의미합니다. 흐름 제어 데이터의 후속 수신이 불가능하다는 알림을 보내는 것을 포함합니다.

하드웨어 흐름 제어 프로토콜 RTS / CTS (하드웨어 흐름 제어)는 CTS 신호를 사용하여 수신기가 데이터를 수신 할 준비가되지 않은 경우 데이터 전송을 중지 할 수 있습니다 (그림 2.9). 송신기는 CTS 라인이 켜져있을 때만 다음 바이트를 "해제"합니다. CTS 신호에 의해 이미 전송되기 시작한 바이트를 지연시키는 것은 불가능합니다 (이는 전송의 무결성을 보장합니다). 하드웨어 프로토콜은 수신기의 상태에 대한 송신기의 가장 빠른 응답을 제공합니다. 비동기식 송수신기 마이크로 회로는 수신부에 적어도 두 개의 레지스터를 가지고 있습니다.

다음 전송을 수신하고, 수신 된 바이트가 판독되는 저장을위한 시프트. 이를 통해 데이터 손실없이 하드웨어 프로토콜을 교환 할 수 있습니다.

하드웨어 프로토콜은 프린터와 플로터를 지원하는 경우 프린터와 플로터를 연결할 때 사용하기 편리합니다 (그림 2.10). 두 대의 컴퓨터를 직접 연결 (모뎀없이)하려면 하드웨어 프로토콜에 RTS-CTS 회선의 상호 연결이 필요합니다.

하드웨어 프로토콜을 사용하지 않는 경우 RTS-CTS 점퍼를 사용하여 CTS 회선에서 전송 터미널이 "켜짐"상태 여야합니다. 그렇지 않으면 송신기가 무음이됩니다.

XON / XOFF 흐름 제어 소프트웨어 프로토콜 양방향 데이터 채널을 가정합니다. 프로토콜은 다음과 같이 작동합니다. 데이터를 수신하는 장치가 더 이상 데이터를 수신 할 수없는 이유를 감지하면 역방향 직렬 채널을 통해 바이트 문자를 보냅니다. Xoff (13 시간). 이 기호를 승인 한 반대 장치는 전송을 일시 중지합니다. 수신 장치가 다시 데이터를 수신 할 준비가되면 문자를 보냅니다.

Xon (llh) 상대 장치가 전송을 재개하는 것을 수락함으로써. 하드웨어 프로토콜과 비교하여 수신기의 상태 변화에 대한 송신기의 응답 시간은 적어도 심볼이 전송 될 때 증가한다 (XON 또는 XOFF) 문자를 수신하기위한 송신기 프로그램의 응답 시간을 더한 것 (그림 2.11). 무손실 데이터는 수신 된 데이터의 추가 버퍼를 갖고 미리 사용할 수없는 시그널링 (버퍼에 여유 공간이 있음)을 갖는 수신기에 의해서만 수신 될 수있다.

소프트웨어 프로토콜의 장점은 인터페이스 제어 신호를 전송할 필요가 없다는 것입니다. 양방향 교환을위한 최소 케이블은 3 개의 와이어 만 가질 수 있습니다 (그림 2.8a 참조). 버퍼 및 긴 반응 시간 (신호 대기로 인해 채널의 전체 성능이 저하됨) 외에 단점 XON) 전이중 교환 모드를 구현하기가 어렵습니다. 이 경우, 흐름 제어 심볼은 수신 된 데이터 스트림으로부터 추출 (및 처리)되어야하며, 이는 전송 된 심볼 세트를 제한한다. 프로토콜과 프린터 (플로터)를 연결하기위한 최소 케이블 옵션 XON / XOFF 그림. 2.12.

PU와 OS에서 지원하는이 두 가지 표준 프로토콜 외에도 다른 프로토콜이 있습니다. 일부 직렬 플로터는 소프트웨어 제어를 사용하지만 비표준 문자를 보냅니다. XON / XOFF, 그러나 단어들 (ASCII 라인). 이러한 교환은 프로토콜의 시스템 지원 수준에서 실질적으로 지원되지 않습니다 (이 플로터는 응용 프로그램과 직접 "통신"). 물론 COM 포트 드라이버 (인터셉터)를 작성할 수 있습니다. INT 14 시간) 그러나 출력 장치에서 문자 메시지를 처리 \u200b\u200b할 필요는 대개 시스템 프로그래머를 기쁘게하지 않습니다. 연결 용 케이블은 그림 1에 표시된 케이블과 일치합니다. 2.12.

2.3. 전류 루프 인터페이스

직렬 인터페이스의 일반적인 옵션은 전류 루프입니다. 전기 신호는 공통 와이어에 대한 전압 레벨이 아니라 현재 수신기와 송신기를 연결하는 2 선식 논리 장치 ( "온"상태)는 20mA의 전류 흐름에 해당하고 논리 영은 전류 부족에 해당합니다. 설명 된 비동기 전송 형식에 대한 신호의 이러한 표현은 라인 브레이크를 검출 할 수있게한다-수신기는 정지 비트가없는 것을 알 것이다 (라인 브레이크는 일정한 논리적 0으로 작용한다).

현재 루프는 일반적으로 갈바니 절연 장치 회로에서 수신기의 입력 회로. 루프의 전류 소스는 송신기입니다 (이 옵션을 활성 송신기라고합니다). 수신기 (액티브 리시버)로부터 전력을 수신 할 수있는 한편, 송신기 출력 키는 나머지 송신기 회로로부터 전기적으로 분리 될 수 있습니다. 단순화 된 옵션은 갈바닉 절연없이 존재하지만 인터페이스의 성능이 저하 된 경우입니다. 전기적으로 절연 된 전류 루프는 신호가 최대 몇 킬로미터 거리에서 전송 될 수 있도록합니다. 거리는 전선 쌍의 저항과 간섭 수준에 따라 결정됩니다. 인터페이스에는 각 신호마다 한 쌍의 전선이 필요하므로 일반적으로 두 개의 인터페이스 신호 만 사용됩니다. 양방향 교환의 경우, 송수신 된 데이터의 신호 만 사용되며 흐름을 제어하기 위해 프로그램 방법이 사용됩니다 XON / XOFF. 양방향 교환이 필요하지 않은 경우 하나의 데이터 라인을 사용하고 흐름을 제어하기 위해 리턴 라인은 CTS 신호 (하드웨어 프로토콜) 또는 다가오는 데이터 라인 (소프트웨어 프로토콜)에 사용됩니다.

신호 변환 RS-232C 간단한 회로를 사용하여 전류 루프에 연결할 수 있습니다 (그림 2.13). 여기서 프린터는 전류 흐름을 통해 하드웨어 흐름 제어를 통해 COM 포트에 연결됩니다. COM 포트의 입력 신호에 필요한 바이폴라 신호를 얻기 위해 인터페이스에서 전원이 공급됩니다.

적절한 소프트웨어를 사용하면 단일 전류 루프가 두 장치간에 양방향 반이중 통신을 제공 할 수 있습니다. 동시에, 각 수신기는 채널의 반대편에있는 송신기의 신호와 송신기의 신호를 모두 "듣습니다". 통신 패킷에 의해 단순히 에코로 간주됩니다. 오류없이 수신하려면 송신기가 교대로 작동해야합니다.

2.4. 미디 인터페이스

디지털 악기 인터페이스 미디(악기 디지털 인터페이스)는 31.25Kbps의 전송 주파수를 갖는 양방향 직렬 비동기 인터페이스입니다. 1983 년에 개발 된이 인터페이스는 컴퓨터, 신디사이저, 녹음 및 재생 장치, 믹서, 특수 효과 장치 및 기타 전자 음악 장비와의 인터페이스를위한 사실상의 표준이되었습니다.

인터페이스가 적용됩니다 이러한 루프 10 mA 입력 회로의 갈바닉 절연으로 (아마도 5mA). 이는 인터페이스 케이블을 통해 연결된 장치의 "회로 랜드"연결을 제거하여 사운드 장비에 매우 바람직하지 않은 간섭을 제거합니다. 전송 주파수의 선택에 의해 간섭 주파수도 감소하는데, 이는 디지털 사운드 기록에 채택 된 양자화 주파수 값 중 하나와 일치한다.

비동기 패키지 시작 비트, 8 비트 정보 및 1 정지 비트를 포함하며 패리티는 없습니다. 전송의 상위 비트는 명령 / 데이터 표시입니다. 0 값은 최하위 비트에 7 개의 데이터 비트가 있음을 나타냅니다. 단일 값에서 비트에는 팀 코드 비트는 채널 번호. 명령은 특정 채널로 보내거나 주소없이 브로드 캐스트 할 수 있습니다. 마지막 그룹에는 장치를 동기화하는 시작, 중지 및 타임 스탬프 명령이 포함됩니다 (동기화 시스템) 미디 싱크 그리고 MTS-MIDI 타임 코드).

인터페이스는 세 가지 유형의 포트를 정의합니다. MIDI-In, MIDI-Out nMIDI- 쓰루.

미디 인 입력 포트 "10 mA 전류 루프"인터페이스의 입력을 나타내며, 최소 2 μs의 속도를 가진 옵토 커플러에 의해 수신기로부터 전기적으로 절연됩니다. 장치는이 입력에서 정보 흐름을 모니터링하고 명령 및 데이터로 처리됩니다.

미디 아웃 포트 는 장치 회로에 전기적으로 연결된 10mA 전류원의 출력을 나타냅니다. 제한 저항은 접지 또는 5V 소스로 단락 될 때 출력 회로가 손상되지 않도록 보호합니다이 장치의 정보 스트림이 출력됩니다. 스트림은 변환 된 입력 스트림을 포함 할 수 있습니다.

대중 교통 포트를 통한 MIDI (선택 사항) 입력 신호를 릴레이하는 역할을합니다.

커넥터로는 가정용 오디오 장비에서 일반적으로 사용되는 5 핀 DIN 커넥터가 사용됩니다. 소켓은 모든 장치에 설치되고 플러그는 케이블에 설치됩니다. 모든 MIDI 연결 케이블이 통합되었습니다 (그림 2.14). 핀 2-케이블 쉴드-트랜스미터 측 (커넥터)의 공통 와이어에만 연결 미디 아웃 그리고 미디 스루).

커넥터 근처에 표시된 입력 및 출력의 레이블에는 해석이 다릅니다. 일부 제조업체는이 장치의 커넥터 기능에 따라 "In"또는 "Out"을 쓴 다음 (올바른 경우) 모든 케이블은 "In"및 "Out"을 연결합니다. 다른 사람들은 서명이 연결된 장치의 기능을 나타내야한다고 생각합니다. 그런 다음 케이블은 "In"- "In"및 "Out"- "Out"으로 커넥터를 연결합니다.

인터페이스를 사용하면 로컬 네트워크에서 최대 16 개의 장치 그룹을 결합 할 수 있습니다. 토폴로지는 다음 규칙을 따라야합니다.

입구 미디 인 하나의 장치를 출력에 연결해야합니다 미디 아웃 또는 미디 스루 다른. MIDI 네트워크를 계획 할 때는 정보 흐름과 장치 통신에 따라 안내해야합니다. 제어 장치 (키보드, 시퀀서 (재생 모드), 동기화 소스)는 제어 대상 장치 앞에 있어야합니다. 양방향 교환이 필요한 장치는 링으로 연결됩니다. 여러 입력 스트림을 논리적으로 하나의 출력으로 전환 할 수있는 특수 멀티플렉서를 사용할 수 있습니다. 링의 축퇴 된 경우는 두 장치의 양방향 연결입니다. 몇 가지 연결 옵션이 그림에 나와 있습니다. 2.15.

PC에는 대부분의 사운드 어댑터에 MIDI 포트가 있으며 신호는 게임 어댑터 커넥터의 사용되지 않는 핀 (12 및 15)으로 출력됩니다. MIDI 장치를 연결하려면 어댑터 어댑터 "현재 루프"인터페이스를 구현합니다. 어댑터 어댑터는 일반적으로 특수 케이블에 내장되어 있으며 회로는 그림 1에 나와 있습니다. 2.16. 일부 PC 모델에는 내장 어댑터 및 표준 5 핀 MIDI 커넥터가 있습니다.

PC는 컨트롤러에 MIDI 호환 포트를 사용합니다 MPU-401 UART 모드에서 (Roland). 입출력 공간에서 MPU-401 인접한 두 주소를 차지 MPU (보통 330 시간) MPU + 1 :

"» 포트 데이터 (주소 MPU + 0)- MIDI 인터페이스를 통해 송수신되는 바이트 쓰기 및 읽기 포트 상태 / 명령 (주소 MPU + 1)- 읽기 상태 / 쓰기 명령 (쓰기-지능형 모드 전용). 다음 비트는 상태 바이트에 정의되어 있습니다.

비트 7- DSR (데이터 세트 준비)-가용성 (DSR-0) 읽을 데이터를 받았습니다. 수신 된 모든 바이트를 데이터 레지스터에서 읽을 때 비트가 "I"로 설정됩니다.

비트 6- DRR (데이터 읽기 준비)-준비 (DRR \u003d 0)데이터 레지스터 또는 명령에 쓰는 UART 수신기에 읽지 않은 바이트의 데이터가 있으면 쓰기 준비 상태가 발생하지 않습니다.

일부 마더 보드는 BIOS를 통해 구성하여 COM 포트에 사용되는 UART를 MIDI 포트 모드로 설정할 수있는 LSI 인터페이스 컨트롤러를 사용합니다.